1.6.1. Setting Up the Design Examples

To set up the design examples, follow these steps:

- Unzip and untar the design examples at the project directory.

Note:

Altera recommends you to untar the example design in Linux environment. The VCS simulation script may become unrecognized or non-executable if the project archive was unzip in Windows environment.

- Launch the Quartus II software and open the following project file:

-

altera_eth_1g10g_top.qpf—for Scalable Multispeed 10G Ethernet MAC using 1G/10G PHY without IEEE 1588v2.

-

altera_eth_top.qpf—for Scalable Multispeed 10G Ethernet MAC using 1G/10G PHY with IEEE 1588v2.

-

- Click Start Compilation on the Processing menu to compile the design example.

- Configure the FPGA on Stratix V GX Transceiver SI Development Board using either:

- altera_eth_1g10g_top.sof—for Scalable Multispeed 10G Ethernet MAC using 1G/10G PHY without IEEE 1588v2.

- altera_eth_top.sof—for Scalable Multispeed 10G Ethernet MAC using 1G/10G PHY with IEEE1588v2.

- After configuration is done, open the Clock Control tool from kits\stratixVGX_5sgxea7nf40_si\examples\board_test_system\ClockControl.exe

The Clock Control tool that is shipped with the “Installation Kit” for Stratix V GX Transceiver SI Development Board.

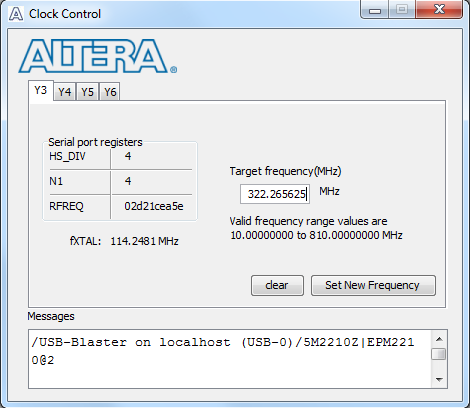

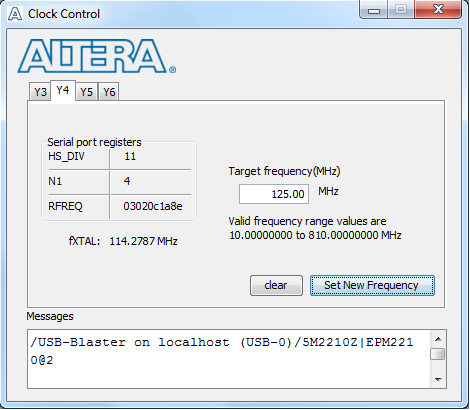

- Set the new frequency for Y3 and Y4 as shown below:

- Y3: 322.265625 MHz

- Y4: 125.00MHz

Figure 3. Clock Control Settings for Y3 Figure 4. Clock Control Settings for Y4

Figure 4. Clock Control Settings for Y4

- Press PB0 push button to reset the system.

Note: System must be hard reset after configuration done.

- On Quartus II Tools menu, click on System Debugging Tools and then launch System Console.

- In the System Console command shell, change the directory to either:

- SystemConsole_wo1588—for Scalable Multispeed 10G Ethernet MAC using 1G/10G PHY without IEEE 1588v2

- SystemConsole—for Scalable Multispeed 10G Ethernet MAC using 1G/10G PHY with IEEE 1588v2

- Run the command source main.tcl to initialize the reference design command list.

- Perform the following test by running the command in the System Console command shell:

- PHY internal serial loopback

Command: TEST_PHYSERIAL_LOOPBACK {channel speed_test burst_size}Example: TEST_PHYSERIAL_LOOPBACK 0 1G 1000

- SMA loopback

Command:

- TEST_SMA_LOOPBACK {channel speed_test burst_size}—for Scalable Multispeed 10G Ethernet MAC using 1G/10G PHY without IEEE 1588v2

Note: Channel 1 is assigned to SFP+ by default. To test Channel 1, you need to reassign it to SMA port.

- TEST_SMA_LB {channel speed_test burst_size}—for Scalable Multispeed 10G Ethernet MAC using 1G/10G PHY with IEEE 1588v2

Example: TEST_SMA_LOOPBACK 0 1G 1000 - TEST_SMA_LOOPBACK {channel speed_test burst_size}—for Scalable Multispeed 10G Ethernet MAC using 1G/10G PHY without IEEE 1588v2

- SMA loopback between 2 channels (for Scalable Multispeed 10G Ethernet MAC using 1G/10G PHY with IEEE 1588v2)

Command: TEST_1588 {from_channel to_channel speed_test}Example: TEST_1588 0 1 1G

Note:For Scalable Multispeed 10G Ethernet MAC using 1G/10G PHY without IEEE 1588v2, Channel 0 is assigned to SMA (GXB_RXL_17 & GXB_TXL_17) and Channel 1 is assigned to SFP+ by default.

For Scalable Multispeed 10G Ethernet MAC using 1G/10G PHY with IEEE 1588v2, Channel 0 is assigned to SMA (GXB_RXL_17 & GXB_TXL_17) and Channel 1 is assigned to SMA (GXB_RXL_16 & GXB_TXL_16) by default.

- PHY internal serial loopback