External Memory Interfaces (EMIF) IP User Guide: Agilex™ 3 FPGAs and SoCs

A newer version of this document is available. Customers should click here to go to the newest version.

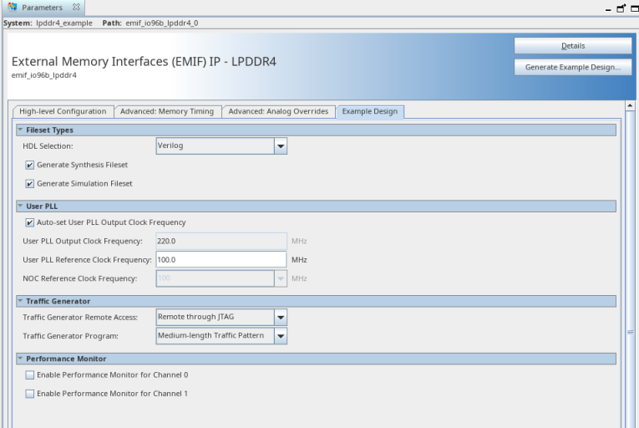

3.5.4. Example Design Tab

This tab contains four groups of parameters: Fileset Types, User PLL, Traffic Generator, and Performance Monitor. The tables which follow provide descriptions of the parameters on this tab.

| Parameter Name | Description |

|---|---|

| HDL Selection | This option lets you choose the format of HDL in which generated simulation and synthesis files are created. You can select either Verilog or VHDL. Default value is VERILOG Legal values are: VERILOG, VHDL (Identifier: EX_DESIGN_HDL_FORMAT) |

| Generate Synthesis Fileset | Generate Synthesis Example Design. Default value is true (Identifier: EX_DESIGN_GEN_SYNTH) |

| Generate Simulation Fileset | Generate Simulation Example Design. Default value is true (Identifier: EX_DESIGN_GEN_SIM) |

| Parameter Name | Description |

|---|---|

| Auto-set User PLL Output Clock Frequency | if true, let IP select a reference clock frequency for the user PLL in the example design; if false, let user set a custom value for this parameter. Default value is true (Identifier: EX_DESIGN_USER_PLL_OUTPUT_FREQ_MHZ_AUTOSET_EN) |

| User PLL Output Clock Frequency | Frequency of the core clock in MHz. This clock drives the traffic generator and NoC initiator (If in NoC mode). Default value is 570 (Identifier: EX_DESIGN_USER_PLL_OUTPUT_FREQ_MHZ) |

| User PLL Reference Clock Frequency | PLL reference clock frequency in MHz for PLL supplying the core clock. Default value is 100 (Identifier: EX_DESIGN_USER_PLL_REFCLK_FREQ_MHZ) |

| NOC Reference Clock Frequency | Reference Clock Frequency for the NOC control IP. Default value is 100 Legal values are: 25, 100, 125 (Identifier: EX_DESIGN_NOC_PLL_REFCLK_FREQ_MHZ) |

| Parameter Name | Description |

|---|---|

| Traffic Generator Remote Access | Specifies whether the Traffic Generator control and status registers are accessible via JTAG, exported to the fabric, or just disabled. Default value is JTAG Legal values are: EXPORT, JTAG (Identifier: EX_DESIGN_TG_CSR_ACCESS_MODE) |

| Traffic Generator Program | Specifies the traffic pattern to be run. Default value is MEDIUM Legal values are: SHORT, MEDIUM, LONG, INFINITE (Identifier: EX_DESIGN_TG_PROGRAM) |

| Parameter Name | Description |

|---|---|

| Enable Performance Monitor for Channel 0 | If true, example design will include a Performance Monitor instance connected to Channel 0. Default value is false (Identifier: EX_DESIGN_PMON_CH0_EN) |

| Enable Performance Monitor for Channel 1 | If true, example design will include a Performance Monitor instance connected to Channel 1. Default value is false (Identifier: EX_DESIGN_PMON_CH1_EN) |