A newer version of this document is available. Customers should click here to go to the newest version.

1. Agilex™ 5 Embedded Memory Overview

2. Agilex™ 5 Embedded Memory Architecture and Features

3. Agilex™ 5 Embedded Memory Design Considerations

4. Agilex™ 5 Embedded Memory IP References

5. Agilex™ 5 Embedded Memory Debugging

6. Document Revision History for the Embedded Memory User Guide: Agilex™ 5 FPGAs and SoCs

2.1. Byte Enable in Agilex™ 5 Embedded Memory Blocks

2.2. Address Clock Enable Support

2.3. Asynchronous Clear and Synchronous Clear

2.4. Memory Blocks Error Correction Code (ECC) Support

2.5. Agilex™ 5 Embedded Memory Clocking Modes

2.6. Agilex™ 5 Embedded Memory Configurations

2.7. Force-to-Zero

2.8. Coherent Read Memory

2.9. Freeze Logic

2.10. True Dual Port Dual Clock Emulator

2.11. Initial Value of Read and Write Address Registers

2.12. Timing/Power Optimization Feature in M20K Blocks

3.1. Consider the Memory Block Selection

3.2. Consider the Concurrent Read Behavior

3.3. Customize Read-During-Write Behavior

3.4. Consider Power-Up State and Memory Initialization

3.5. Reduce Power Consumption

3.6. Avoid Providing Non-Deterministic Input

3.7. Avoid Changing Clock Signals and Other Control Signals Simultaneously

3.8. Advanced Settings in Quartus® Prime Software for Memory

3.9. Consider the Memory Depth Setting

3.10. Consider Registering the Memory Output

4.1.1. Release Information for RAM and ROM Intel® FPGA IPs

4.1.2. RAM: 1-PORT Intel® FPGA IP Parameters

4.1.3. RAM: 2-PORT Intel® FPGA IP Parameters

4.1.4. RAM: 4-PORT Intel® FPGA IP Parameters

4.1.5. ROM: 1-PORT Intel® FPGA IP Parameters

4.1.6. ROM: 2-PORT Intel® FPGA IP Parameters

4.1.7. Changing Parameter Settings Manually

4.1.8. RAM and ROM Interface Signals

4.2.1. Release Information for FIFO Intel® FPGA IP

4.2.2. Configuration Methods

4.2.3. Specifications

4.2.4. FIFO Functional Timing Requirements

4.2.5. SCFIFO ALMOST_EMPTY Functional Timing

4.2.6. FIFO Output Status Flag and Latency

4.2.7. FIFO Metastability Protection and Related Options

4.2.8. FIFO Synchronous Clear and Asynchronous Clear Effect

4.2.9. SCFIFO and DCFIFO Show-Ahead Mode

4.2.10. Different Input and Output Width

4.2.11. DCFIFO Timing Constraint Setting

4.2.12. Coding Example for Manual Instantiation

4.2.13. Instantiation Template

4.2.14. Design Example

4.2.15. Gray-Code Counter Transfer at the Clock Domain Crossing

4.2.16. Guidelines for Embedded Memory ECC Feature

4.2.17. FIFO Intel® FPGA IP Parameters

4.2.18. Reset Scheme

4.3.1. Release Information for Shift Register (RAM-based) Intel® FPGA IP

4.3.2. Shift Register (RAM-based) Intel® FPGA IP Features

4.3.3. Shift Register (RAM-based) Intel® FPGA IP General Description

4.3.4. Shift Register (RAM-based) Intel® FPGA IP Parameter Settings

4.3.5. Shift Register Ports and Parameters Setting

4.2.9. SCFIFO and DCFIFO Show-Ahead Mode

You can set the read request/rdreq signal read access behavior by selecting normal or show-ahead mode.

For normal mode, the FIFO Intel® FPGA IP core treats the rdreq port as a normal read request that only performs read operation when the port is asserted.

For show-ahead mode, the FIFO Intel® FPGA IP core treats the rdreq port as a read-acknowledge that automatically outputs the first word of valid data in the FIFO Intel® FPGA IP core (when the empty is low) without asserting the rdreq signal. Asserting the rdreq signal causes the FIFO Intel® FPGA IP core to output the next data word, if available.

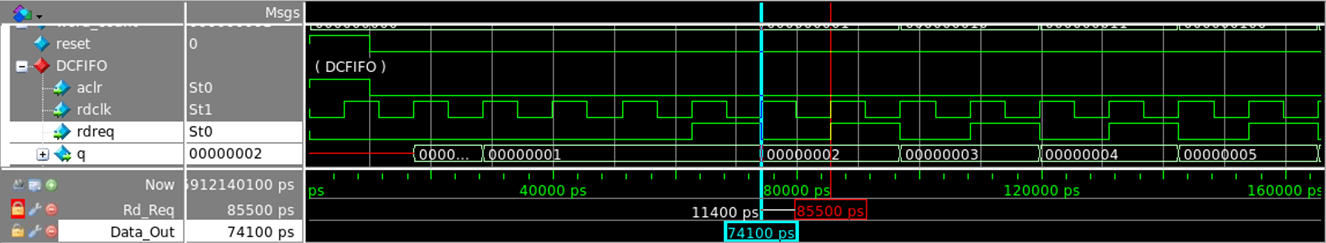

Figure 34. Normal Mode Waveform

Data appears after the rdreq asserted.

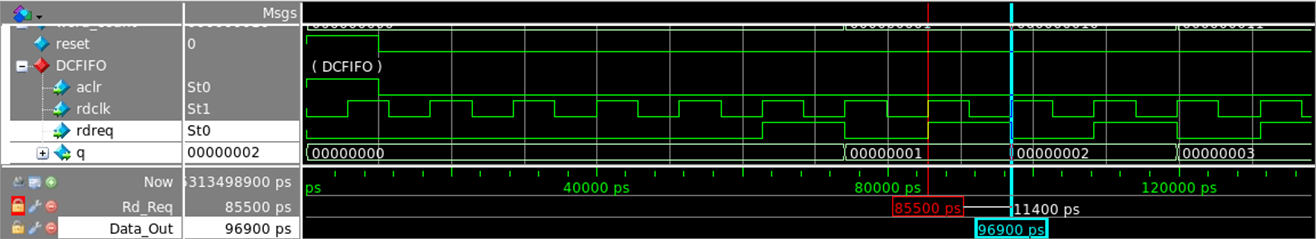

Figure 35. Show-Ahead Mode Waveform

Data appears before the rdreq asserted.