A newer version of this document is available. Customers should click here to go to the newest version.

1. About the Nios® V Embedded Processor

2. Nios® V Processor Hardware System Design with Intel® Quartus® Prime Software and Platform Designer

3. Nios® V Processor Software System Design

4. Nios® V Processor Configuration and Booting Solutions

5. Nios® V Processor - Using the MicroC/TCP-IP Stack

6. Nios® V Processor Debugging, Verifying, and Simulating

7. Nios® V Processor — Remote System Update

8. Nios® V Processor — Using Custom Instruction

9. Nios® V Embedded Processor Design Handbook Archives

10. Document Revision History for the Nios® V Embedded Processor Design Handbook

4.1. Introduction

4.2. Linking Applications

4.3. Nios® V Processor Booting Methods

4.4. Introduction to Nios® V Processor Booting Methods

4.5. Nios® V Processor Booting from Configuration QSPI Flash

4.6. Nios® V Processor Booting from On-Chip Memory (OCRAM)

4.7. Nios® V Processor Booting from Tightly Coupled Memory (TCM)

4.8. Summary of Nios® V Processor Vector Configuration and BSP Settings

6.5.1. Prerequisites

6.5.2. Setting Up and Generating Your Simulation Environment in Platform Designer

6.5.3. Creating Nios V Processor Software

6.5.4. Generating Memory Initialization File

6.5.5. Generating System Simulation Files

6.5.6. Running Simulation in the QuestaSim Simulator Using Command Line

6.5.2. Setting Up and Generating Your Simulation Environment in Platform Designer

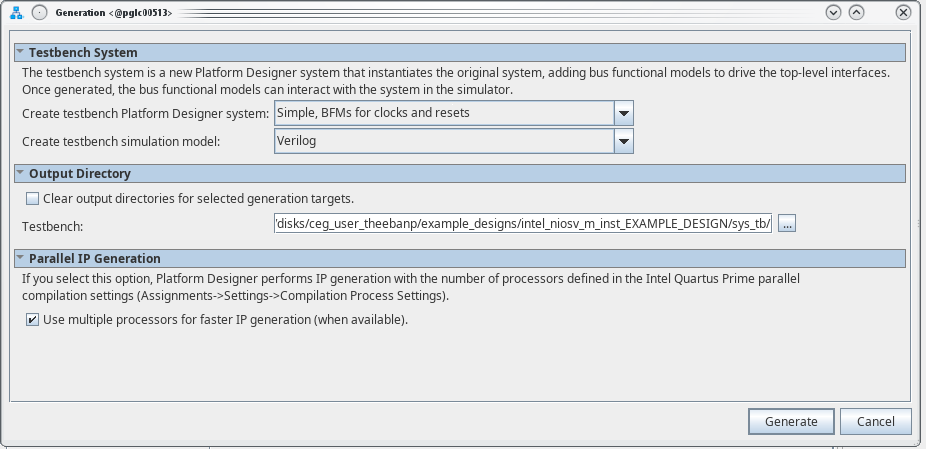

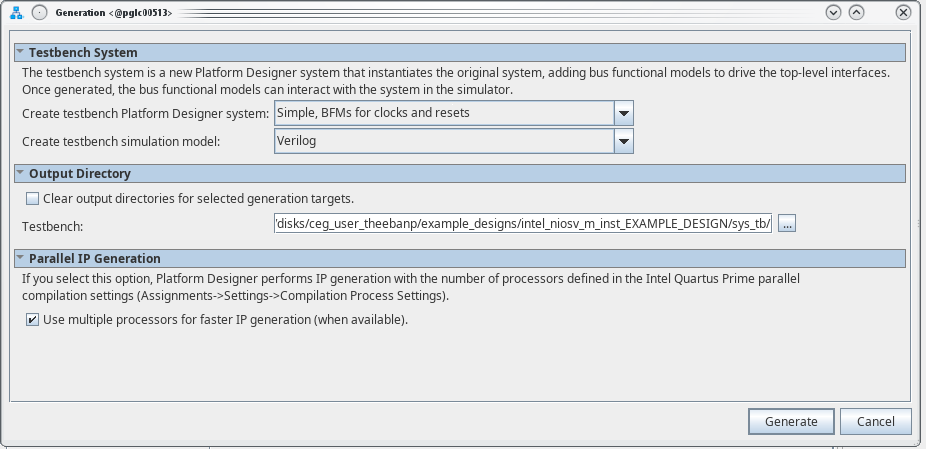

To generate simulation files, perform the following steps:

- Start the Intel Quartus Prime software and open the Platform Designer from the Tools menu.

- Open the <your project design>.qsys file.

Note: Ensure that you have completed building your Platform Designer system before generating the simulation models

- In Platform Designer, navigate to Generate > Generate Testbench System.

- On the Generation window, set the following parameters to these values:

- Create testbench Platform Designer system— Standard, BFMs for standard Platform Designer interfaces.

Note: If your system has exported ports other than the clock and reset, choose Standard, BFMs for standard Avalon interfaces.

- Create testbench simulation model—Verilog

- Select Use multiple processors for faster IP generation (when available).

- Create testbench Platform Designer system— Standard, BFMs for standard Platform Designer interfaces.

- Click Generate, and Save, if prompted.

Figure 107. Testbench Generation