Intel® Quartus® Prime Pro Edition User Guide: Third-party Simulation

ID

683870

Date

12/21/2022

Public

A newer version of this document is available. Customers should click here to go to the newest version.

1. Answers to Top FAQs

2. Intel FPGA Simulation Basics

3. Questa* Intel® FPGA Edition, ModelSim* , and QuestaSim* Simulator Support

4. Synopsys VCS* and VCS MX Support

5. Aldec Active-HDL and Riviera-PRO Support

6. Cadence Xcelium* Parallel Simulator Support

7. Intel® Quartus® Prime Pro Edition User Guide Third-party Simulation Archive

A. Intel® Quartus® Prime Pro Edition User Guides

3.1. Quick Start Example (ModelSim with Verilog)

3.2. Questa* Intel® FPGA Edition, ModelSim, and QuestaSim Simulator Guidelines

3.3. ModelSim Simulation Setup Script Example

3.4. Sourcing ModelSim* or QuestaSim Simulator Setup Scripts

3.5. Unsupported Features

3.6. Questa* Intel® FPGA Edition, ModelSim* , and QuestaSim* Simulator Support Revision History

3.2.1. Using Questa* Intel® FPGA Edition Precompiled Libraries

3.2.2. Passing Parameter Information from Verilog HDL to VHDL

3.2.3. Viewing Simulation Messages

3.2.4. Generating Signal Activity Data for Power Analysis

3.2.5. Viewing Simulation Waveforms

3.2.6. Simulating with Questa* Intel® FPGA Edition Waveform Editor

3.2.4. Generating Signal Activity Data for Power Analysis

To generate and use simulation signal activity data for power analysis:

- To run full compilation on your design, click Processing > Start Compilation.

- To specify settings for simulation output, click Assignments > Settings > EDA Tool Settings > Simulation. Select your simulator in Tool name and the Format for output netlist and Output directory.

Figure 6. EDA Tool Settings for Simulation

- Turn on Map illegal HDL characters. This setting directs the EDA Netlist Writer to map illegal characters for VHDL or Verilog HDL, and results in more accurate data for power analysis.

- Click the Power Analyzer Settings page.

- For Intel® Stratix® 10 designs, to generate a Standard Delay Output (.sdo) file that includes back-annotation of delays for power analysis, refer to Generating Standard Delay Output for Power Analysis.

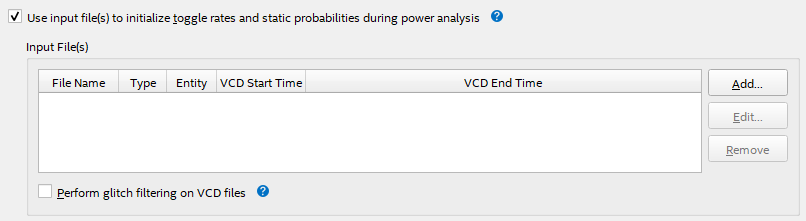

- Under Input file, turn on Use input files to initialize toggle rates and static probabilities during power analysis.

Figure 7. Specifying Power Analysis Input Files

- To specify a .vcd for power analysis, click Add and specify the File name, Entity, and Simulation period for the .vcd, and click OK.

- To enable glitch filtering during power analysis with the .vcd you generate, turn on Perform glitch filtering on VCD files.

- To run the power analysis, click Start on the Power Analysis step in the Compilation Dashboard. View the toggle rates in the power analysis results.

Note: To improve accuracy of power analysis, the Intel® Quartus® Prime EDA Netlist writer can generate a Standard Delay Output (.sdo) file that includes back-annotation of delays for a design's netlist for use during simulation in ModelSim* . Although the .sdo only contains delay estimates and imprecise timing information, including the .sdo in simulation results in a more accurate output .vcd for power analysis. The EDA Netlist Writer currently supports .sdo file generation only for Verilog .vo simulation in the ModelSim* simulator (not Questa* Intel® FPGA Edition) for Intel® Stratix® 10 designs. The EDA Netlist Writer does not currently support .sdo file generation for any other simulator or device family.