Early Power Estimator for Intel® Cyclone® 10 LP FPGAs User Guide

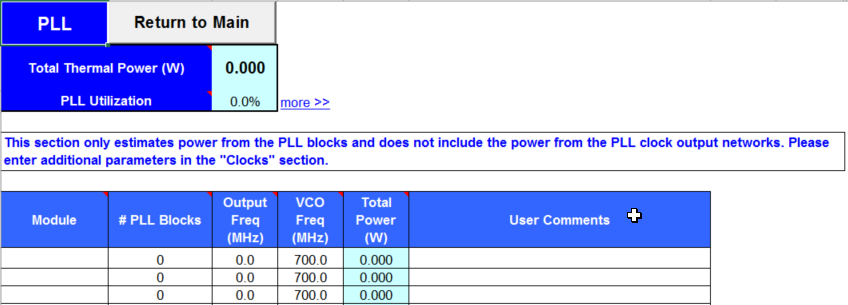

3.6. Cyclone® 10 LP EPE - PLL Worksheet

Cyclone® 10 LP devices feature PLLs for general use. Each row in the PLL worksheet of the Early Power Estimator (EPE) spreadsheet represents one or more PLLs in the device. Enter the maximum output frequency and the VCO frequency for each PLL. You must also specify whether each PLL is an LVDS, fractional, left/right, or top/bottom PLL.

When a PLL drives source synchronous SERDES hardware, it is referred to as an LVDS PLL. If you are using dedicated transmitters or receivers and are using an LVDS PLL to implement serialization or deserialization, specify an LVDS PLL and enter the power information in the PLL worksheet. LVDS PLLs drive LVDS clock trees and dynamic phase alignment (DPA) buses at the voltage-controlled oscillator (VCO) frequency. If an LVDS PLL drives the LVDS hardware only, enter the appropriate VCO frequency and specify an output frequency of 0 MHz. If the LVDS PLL also drives a clock to a pin or to the core, specify that clock frequency as the output frequency.

| Column Heading | Description |

|---|---|

| Module | Specify a name for the PLL in this column. This is an optional value. |

| # PLL Blocks | Enter the number of PLL blocks with the same specific output frequency and VCO frequency combination. |

| Output Freq (MHz) | Enter the maximum output frequency of the PLL (in MHz). The maximum output frequency is reported in the Output Frequency column of the Quartus II Compilation Report. In the Compilation Report, select Fitter and click Resource Section. Select PLL Usage and click Output Frequency. |

| VCO Freq (MHz) | Enter the internal VCO operating frequency for this module. The LVDS PLL drives the LVDS clock tree and DPA bus at this frequency. This frequency includes the VCO post scale counter. |

| VCO Freq (MHz) | Enter the internal VCO operating frequency for general purpose PLL. |

| Total Power (W) | Shows the estimated combined power for VCCA and VCCD (in watts), based on the maximum output frequency and the VCO frequency you entered. This value is automatically calculated. |

| User Comments | Enter any comments. This is an optional entry. |

For more information about the PLLs of the supported device families, refer to the Clock Networks and PLLs section of the Cyclone® 10 LP device handbook.