Early Power Estimator for Intel® Cyclone® 10 LP FPGAs User Guide

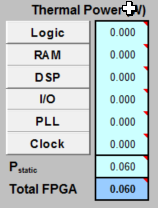

3.1.2. Thermal Power

Total thermal power includes only the thermal component for the I/O section and does not include the external power dissipation, such as from voltage-referenced termination resistors.

The static power (PSTATIC) is the thermal power dissipated on chip, independent of user clocks. PSTATIC includes the leakage power from all FPGA functional blocks, except for I/O DC bias power and transceiver DC bias power, which are accounted for in the I/O and transceiver sections.

PSTATIC is the only thermal power component which varies with junction temperature, selected device, and power characteristics (process).

The following figure shows the total thermal power (W) and PSTATIC consumed by the FPGA. The thermal power for each worksheet is displayed. To see how the thermal power for a worksheet was calculated, click on the button to view the selected worksheet.

| Column Heading | Description |

|---|---|

| Logic | This value shows the dynamic power consumed by adaptive logic modules (ALMs) and associated routing. To view details, click the Logic button. |

| RAM | This value shows the dynamic power consumed by RAM blocks and associated routing. To view details, click the RAM button. |

| DSP | This value shows the dynamic power consumed by digital signal processing (DSP) blocks and associated routing. To view details, click the DSP button. |

| I/O | This value shows the thermal power consumed by I/O pins and associated routing. To view details, click the I/O button. |

| PLL | This value shows the dynamic power consumed by phase-locked loops (PLLs). To view details, click the PLL button. |

| Clock | This value shows the dynamic power consumed by clock networks. To view details, click the Clock button. |

| PSTATIC | This shows the thermal power dissipated on chip, independent of user clocks. This includes the leakage power from all FPGA functional blocks, except for I/O DC bias power and transceiver DC bias power. PSTATIC is affected by junction temperature, selected device, and power characteristics. |

| Total FPGA | This shows the total power dissipated as heat from the FPGA. This does not include power dissipated in off-chip termination resistors. |