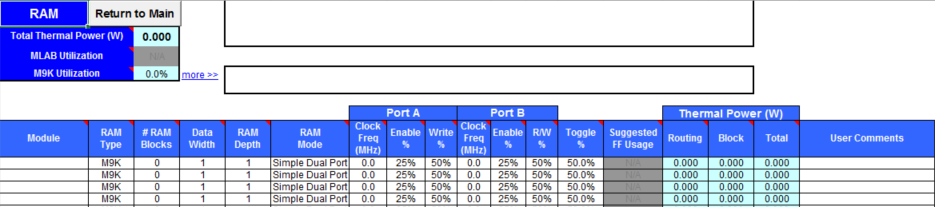

3.3. Cyclone® 10 LP EPE - RAM Worksheet

Each row in the RAM worksheet of the Early Power Estimator (EPE) spreadsheet represents a design module where the RAM blocks are the same type, have the same data width, the same RAM depth (if applicable), the same RAM mode, and the same port parameters. If some or all of the RAM blocks in your design have different configurations, enter the information in different rows. For each design module, enter the type of RAM implemented, the number of RAM blocks, and the RAM block mode.

Each row in the RAM worksheet of the EPE spreadsheet can also represent a logical RAM module that can be physically implemented on more than one RAM block. The EPE spreadsheet implements each logical RAM module with the minimum number of physical RAM blocks, in the most power-efficient way possible, based on the width and depth of the logical instance entered.

You must know how your RAM is implemented by the Quartus® Prime Compiler when you are selecting the RAM block mode. For example, if a ROM is implemented with two ports, it is considered a true dual-port memory and not a ROM. Single-port and ROM implementations only use Port A. Simple dual-port and true dual-port implementations use Port A and Port B.

| Column Heading | Description |

|---|---|

| Module | Enter a name for the RAM module in this column. This is an optional value. |

| RAM Type | Select the implemented RAM type. You can find the RAM type in the Type column of the Quartus® Prime Compilation Report. In the Compilation Report, select Fitter and click Resource Section. Click RAM Summary. |

| #RAM Blocks |

Enter the number of RAM blocks in the module that use the same type and mode and have the same parameter for each port. The parameters for each port are:

You can find the number of RAM blocks in either the memory logic array block (MLAB) or M9K column of the Quartus® Prime Compilation Report. In the Compilation Report, select Fitter and click Resource Section. Click RAM Summary. |

| Data Width | Enter the width of the data for the RAM block. This value is limited based on the RAM type. You can find the width of the RAM block in the Port A Width or the Port B Width column of the Quartus® Prime Compilation Report. In the Compilation Report, select Fitter and click Resource Section. Click RAM Summary. For RAM blocks that have different widths for Port A and Port B, use the larger of the two widths. |

| RAM Depth | Enter the depth of the RAM block in number of words. You can find the depth of the RAM block in the Port A Depth or the Port B Depth column of the Quartus® Prime Compilation Report. In the Compilation Report, select Fitter and click Resource Section. Click RAM Summary. |

| RAM Mode |

Select from the following modes:

The mode is based on how the Quartus® Prime Compiler implements the RAM. If you are unsure how your memory module is implemented, Intel® recommends compiling a test case in the required configuration in the Quartus® Prime software. You can find the RAM mode in the Mode column of the Quartus® Prime Compilation Report. In the Compilation Report, select Fitter and click Resource Section. Click RAM Summary. A single-port RAM has one port with a read and write control signal. A simple dual-port RAM has one read port and one write port. A true dual-port RAM has two ports, each with a read and write control signal. ROMs are read-only single-port RAMs. |

| Port A–Clock Freq (MHz) | Enter the average percentage of time the input clock enable for Port A is active, regardless of the activity on the RAM data and address inputs. The enable percentage ranges from 0 to 100%. The default value is 25%. RAM power is primarily consumed when a clock event occurs. Using a clock enable signal to disable a port when no read or write operation is occurring can result in significant power savings. |

| Port A–Enable | Enter the average percentage of time the input clock enable for Port A is active, regardless of the activity on the RAM data and address inputs. The enable percentage ranges from 0 to 100%. RAM power is primarily consumed when a clock event occurs. Using a clock-enable signal to disable a port when no read or write operation is occurring can result in significant power savings. |

| Port A–Write % | Enter the average percentage of time Port A of the RAM block is in write mode versus read mode. For simple dual-port (1R/1W) RAMs, the write Port A is inactive when not executing a write operation. For single-port and dual-port RAMs, Port A reads when it is not written to. This field is ignored for RAMs in ROM mode. This value must be a percentage number between 0 and 100%. The default value is 50%. |

| Port B–Clock Freq (MHz) | Enter the clock frequency for Port B of the RAM blocks in MHz. This value is limited by the maximum frequency specification for the RAM type and device family. Port B is ignored for RAM blocks in ROM or single-port mode or when the chosen RAM type is MLAB. |

| Port B–Enable % | Enter the average percentage of time the input clock enable for Port B is active, regardless of the activity on the RAM data and address inputs. The enable percentage ranges from 0 to 100%. RAM power is primarily consumed when a clock event occurs. Using a clock-enable signal to disable a port when no read or write operation is occurring can result in significant power savings. |

| Port B–R/W % | For RAM blocks in true dual-port mode, enter the average percentage of time Port B of the RAM block is in write mode versus read mode. For RAM blocks in simple dual-port mode, enter the percentage of time Port B of the RAM block is reading. You cannot write to Port B in simple dual-port mode. Port B is ignored for RAM blocks in ROM or single-port mode or when the chosen RAM type is MLAB. This value must be a percentage number between 0 and 100%. The default value is 50%. |

| Toggle% | The average percentage for how often each block output signal changes value on each clock cycle is multiplied by the clock frequency and enables the percentage to determine the number of transitions per second. This only affects routing power. 50% corresponds to a randomly changing signal. A random signal changes states only half the time. |

| Suggested FF Usage | Displays the number of flipflops that you require to make the MLAB function correctly. The MLAB power in the RAM worksheet does not include the power of the flipflops. If you enter the device resources manually, add the suggested number of flipflops to the Logic worksheet using the same clock frequency. If you have imported the device resources from the EPE file, no action is required. This field is only valid when the chosen RAM type is MLAB. |

| Thermal Power (W)–Routing | This shows the power dissipation due to estimated routing (in watts). Routing power depends on placement and routing, which is a function of design complexity. The values shown represent the routing power based on experimentation of more than 100 designs. For detailed analysis based on your design’s routing, use the Quartus® Prime Power Analyzer. This value is calculated automatically. |

| Thermal Power (W)–Block | This shows the power dissipation due to internal toggling of the RAM (in watts). For accurate analysis based on your design’s exact RAM modes, use the Quartus® Prime Power Analyzer. This value is calculated automatically. |

| Thermal Power (W)–Total | This shows the estimated power in watts, based on your inputs. It is the total power consumed by the RAM blocks and is equal to the routing power and block power. This value is calculated automatically. |

| User Comments | Enter any comments. This is an optional entry. |

For more information about RAM block configurations, refer to the Memory Blocks section of the Cyclone® 10 LP device handbook.