Intel® Quartus® Prime Standard Edition User Guide: Programmer

ID

683528

Date

9/24/2018

Public

1.1. Programming Flow

1.2. Intel® Quartus® Prime Programmer Window

1.3. Programming and Configuration Modes

1.4. Design Security Keys

1.5. Verifying if Programming Files Correspond to a Compilation of the Same Source Files

1.6. Convert Programming Files Dialog Box

1.7. Flash Loaders

1.8. JTAG Debug Mode for Partial Reconfiguration

1.9. Scripting Support

1.10. Programming Intel® FPGA Devices Revision History

1.8.1. Configuring Partial Reconfiguration Bitstream in JTAG Debug Mode

To configure the Partial Reconfiguration bitstream in JTAG debug mode, follow these steps:

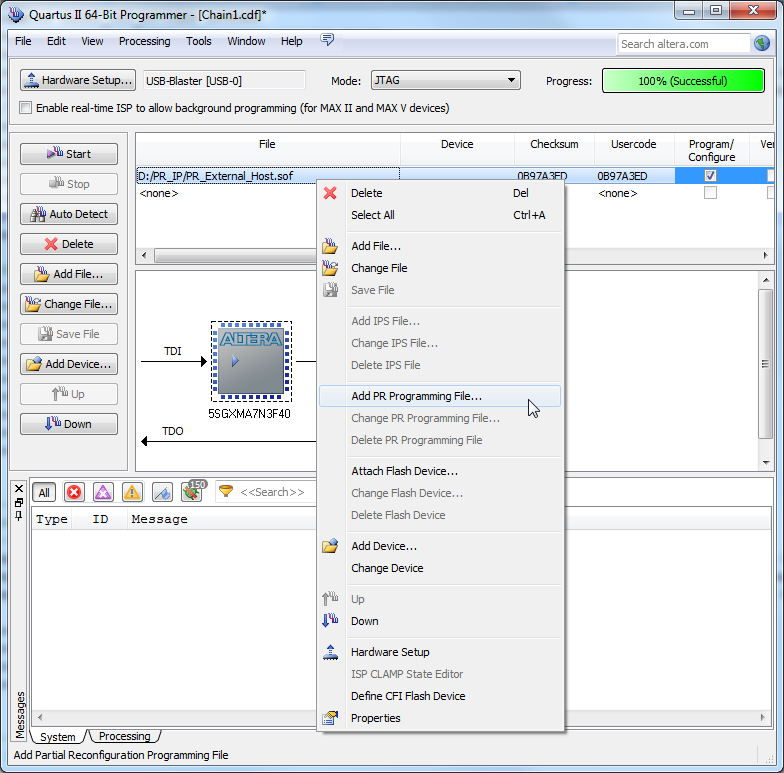

- In the Intel® Quartus® Prime Programmer GUI, right click a highlighted base bitstream (in .sof) and then click Add PR Programming File to add the PR bitstream (.rbf).

Figure 1. Adding PR Programming File

- After adding the PR bitstream, you can change or delete the Partial Reconfiguration programming file by clicking Change PR Programming File or Delete PR Programming File.

Figure 2. Change PR Programming File or Delete PR Programming File

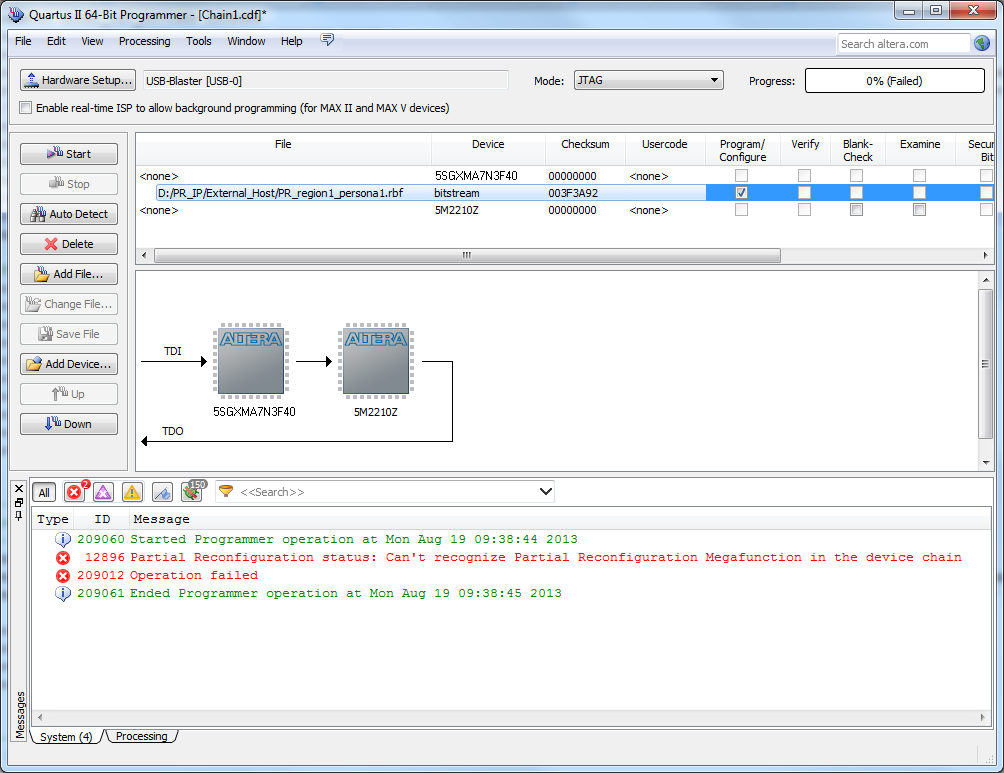

- Click Start to configure the PR bitstream. The Intel® Quartus® Prime Programmer generates an error message if the specified device does not contain the PR IP core in the design (you must instantiate the Partial Reconfiguration IP core in your design to use the JTAG debug mode).

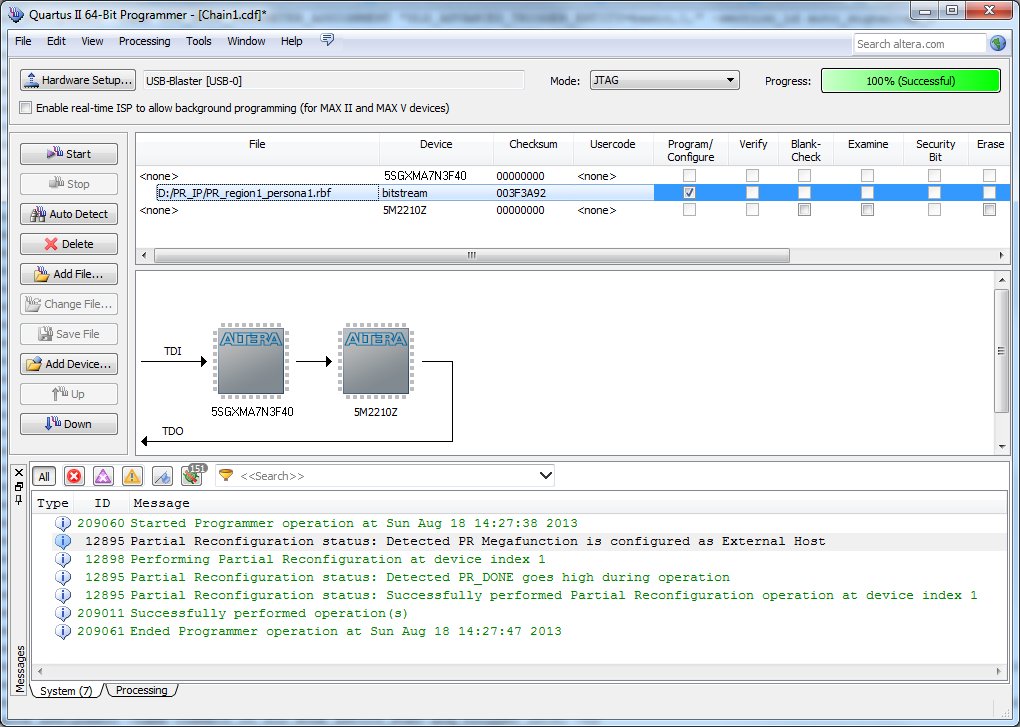

Figure 3. Starting PR Bitstream Configuration

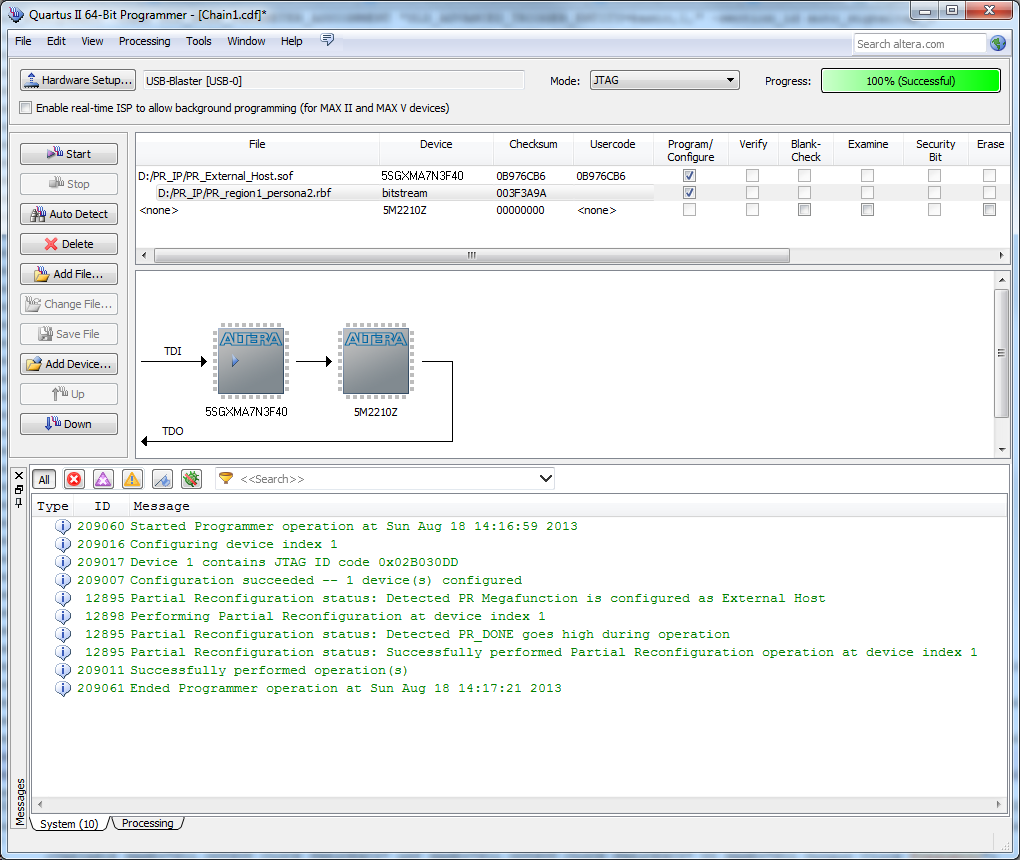

- Configure the valid .rbf in JTAG debug mode with the Intel® Quartus® Prime Programmer.

Figure 4. Configuring Valid .rbf

- The JTAG debug mode is also supported if the PR IP core is pre-programmed on the specified device.

Figure 5. Partial Reconfiguration IP Core Successfully Pre-programmed

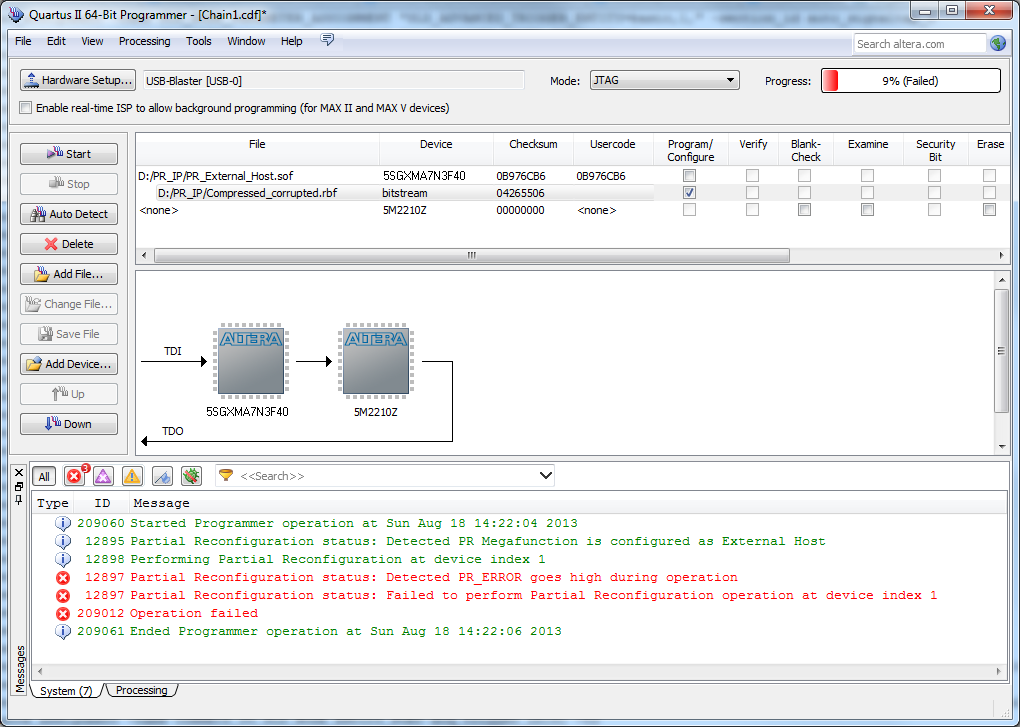

- The Intel® Quartus® Prime Programmer reports error when you try to configure the corrupted .rbf in JTAG debug mode.

Figure 6. Configuring Corrupted .rbf