AN 861: Intel® Stratix® 10 H-Tile PCI Express* Link Hardware Validation

ID

683407

Date

6/29/2018

Public

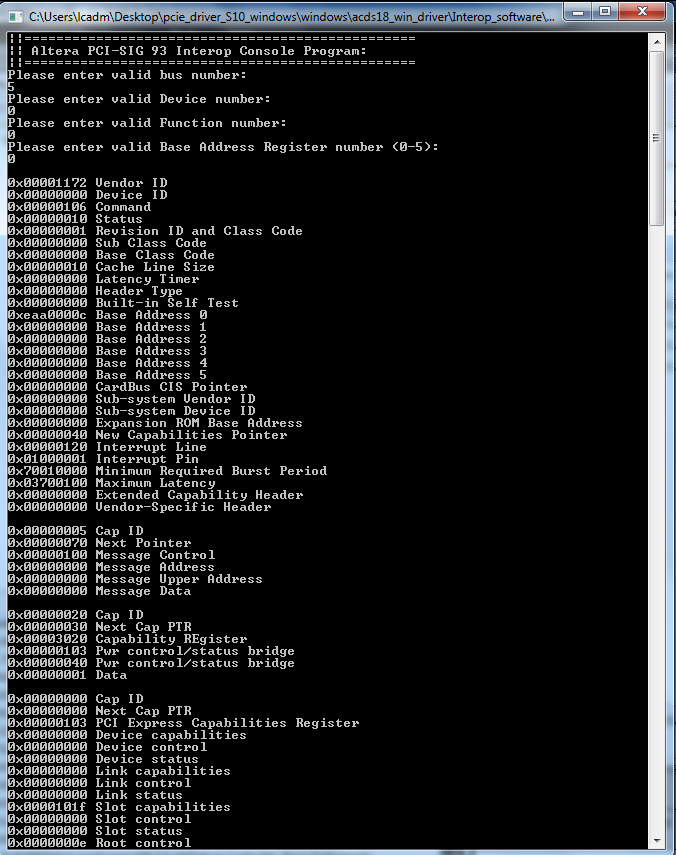

1.4.3.2.2. Running the Windows demo driver with design example

The software application to test the PCI Express* design example on the Intel® Stratix® 10 FPGA Development Kit is available on both 32- and 64-bit Windows platforms. This program performs the following tasks:

- Print the configuration space, lane rate and lane width.

- Write 0x00000000 to the specified BAR at offset 0x00000000 to initialize the memory and read it back.

- Write 0xABCD1234 at offset 0x00000000 of the specified BAR, then read it back and compare.

If successful, the test program displays the message "PASSED".

Follow these steps to perform the PCIe* link test with the Windows demo driver with the design example in hardware:

- In the Interop_software folder, run the Alt_Test.exe.

- When prompted, enter the bus, device and function numbers for your Altera PCI API Driver as shown in the following figure.

Figure 10. Bus, device and function numbers and BAR number entries into the application software

Note: The bus, device and function numbers for your hardware setup may be different.

Note: The bus, device and function numbers for your hardware setup may be different. - Enter the BAR number (0 - 5) that you specified during the parameterization of the Avalon® -ST Intel® Stratix® 10 Hard IP for PCI Express* IP core.

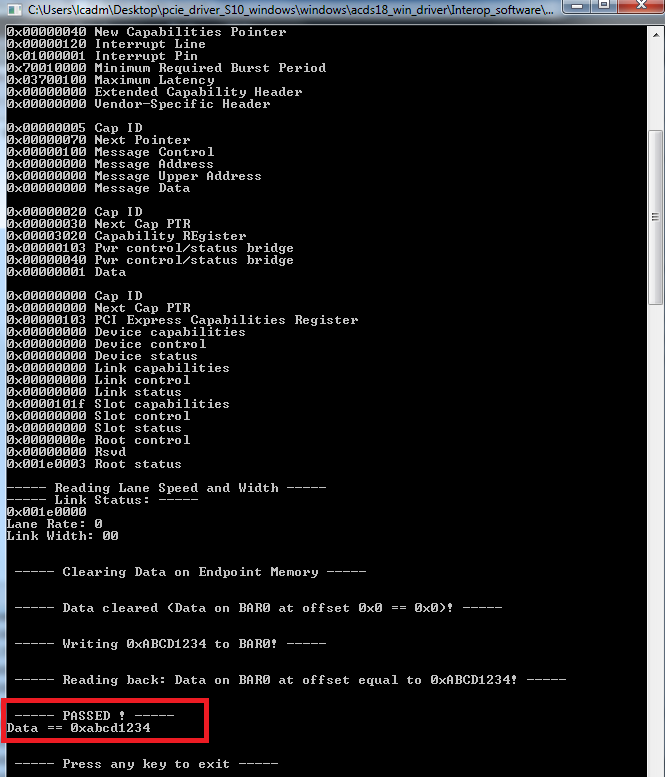

- The Interop software application will proceed with the PCIe* link test.

- If the test is successful, you will see the message "PASSED" as shown in the figure below.

Figure 11. "PASSED" message to indicate a successful link test

Note: There is a known issue with this Windows demo driver. The lane rate and link width are incorrectly displayed as Lane Rate = 0 and Link Width = 00. This issue will be fixed in the future release of the Windows demo driver.

Note: There is a known issue with this Windows demo driver. The lane rate and link width are incorrectly displayed as Lane Rate = 0 and Link Width = 00. This issue will be fixed in the future release of the Windows demo driver.