Intel® High Level Synthesis Compiler Pro Edition: Reference Manual

A newer version of this document is available. Customers should click here to go to the newest version.

7.3. Component Pipelining Control (hls_disable_component_pipelining Attribute)

If running concurrent invocations of your component does not improve throughput, or if you do not intend to invoke your component repeatedly, avoid extra FPGA area utilization by using the hls_disable_component_pipelining component attribute.

When you specify the hls_disable_component_pipelining, the Intel® HLS Compiler generates a simpler, serialized datapath for your component.

#include "HLS/hls.h"

hls_disable_component_pipelining

component void baz ( /* arguments */ ){

// component code

}You can also disable pipelining the datapath of a loop in your component with the disable_loop_pipelining pragma. For more information about this pragma see Loop Pipelining Control (disable_loop_pipelining Pragma).

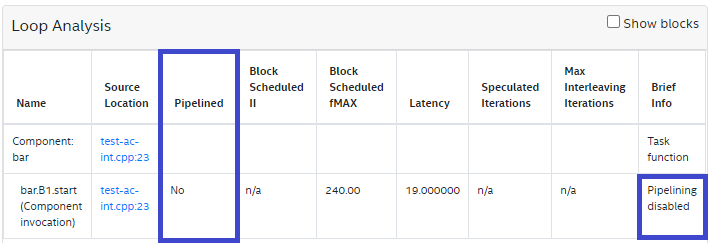

Review the Loop Analysis report in the High-Level Design Reports (report.html) to see component invocations and loops with pipelining disabled: