GTS AXI Streaming IP for PCI Express* Design Example User Guide

ID

817713

Date

10/23/2025

Public

2.1. Directory Structure

2.2. Generating the Design Example

2.3. Simulating the Design Example

2.4. Design Example Simulation Testbench

2.5. Compiling the Design Example

2.6. Hardware and Software Requirements

2.7. Program the FPGA

2.8. Installing the Linux Kernel Driver

2.9. Running the Design Example

A.1.1. ebfm_barwr Procedure

A.1.2. ebfm_barwr_imm Procedure

A.1.3. ebfm_barrd_wait Procedure

A.1.4. ebfm_barrd_nowt Procedure

A.1.5. ebfm_cfgwr_imm_wait Procedure

A.1.6. ebfm_cfgwr_imm_nowt Procedure

A.1.7. ebfm_cfgrd_wait Procedure

A.1.8. ebfm_cfgrd_nowt Procedure

A.1.9. BFM Configuration Procedures

A.1.10. BFM Shared Memory Access Procedures

A.1.11. BFM Log and Message Procedures

A.1.12. Verilog HDL Formatting Functions

2.7. Program the FPGA

Prerequisite: Generate and compile the design example in the Quartus® Prime Pro Edition software before testing it on hardware.

This section describes how to configure the Agilex™ 5 FPGA on the Agilex™ 5 FPGA E-Series 065B Modular Development Kit (ES1).

- Install the Agilex™ 5 FPGA E-Series 065B Modular Development Kit into a PCIe Gen4 x4 slot on the host system, connected to the ATX 6-pins power supply.

- Connect the Agilex™ 5 FPGA E-Series 065B Modular Development Kit to a computer system on which the Quartus® Prime Pro Edition software is installed using the USB cable shipped along with the development kit for FPGA configuration.

- Power on the host system and turn on the power switch on the development kit.

- In the Quartus® Prime Pro Edition software, invoke the Programmer by clicking Tools > Programmer.

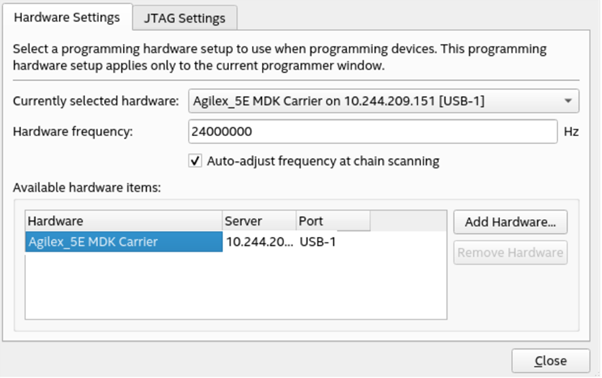

- In the Programmer, click Hardware Setup and verify the Agilex™ 5 FPGA E-Series 065BModular Development Kit is detected in the Hardware Settings tab.

- For Currently selected hardware, select the Agilex™ 5 FPGA E-Series 065B Modular Development Kit and then click Close.

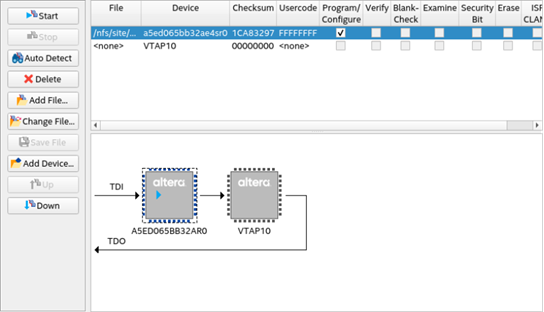

- Click Auto Detect to detect the JTAG device chain.

- Select the target FPGA device in the JTAG chain, click Change File, and select the FPGA configuration file, pcie_ed.sof. Then, click Open.

- Check the Program/Configure option and click Start to start the FPGA configuration.

- Perform a warm reboot for the host system once the Agilex™ 5 FPGA is successfully configured.

- Check the enumeration of the PCIe Endpoint device ( Agilex™ 5 FPGA E-Series 065B Modular Development Kit ) on the host system by running the “lspci –d 1172:” command in a Linux Terminal.

Expected result:

BDF Unassigned class [ff00]: Altera Corporation Device 0000 (rev 01)