GTS AXI Streaming IP for PCI Express* Design Example User Guide

ID

817713

Date

10/23/2025

Public

2.1. Directory Structure

2.2. Generating the Design Example

2.3. Simulating the Design Example

2.4. Design Example Simulation Testbench

2.5. Compiling the Design Example

2.6. Hardware and Software Requirements

2.7. Program the FPGA

2.8. Installing the Linux Kernel Driver

2.9. Running the Design Example

A.1.1. ebfm_barwr Procedure

A.1.2. ebfm_barwr_imm Procedure

A.1.3. ebfm_barrd_wait Procedure

A.1.4. ebfm_barrd_nowt Procedure

A.1.5. ebfm_cfgwr_imm_wait Procedure

A.1.6. ebfm_cfgwr_imm_nowt Procedure

A.1.7. ebfm_cfgrd_wait Procedure

A.1.8. ebfm_cfgrd_nowt Procedure

A.1.9. BFM Configuration Procedures

A.1.10. BFM Shared Memory Access Procedures

A.1.11. BFM Log and Message Procedures

A.1.12. Verilog HDL Formatting Functions

2.5. Compiling the Design Example

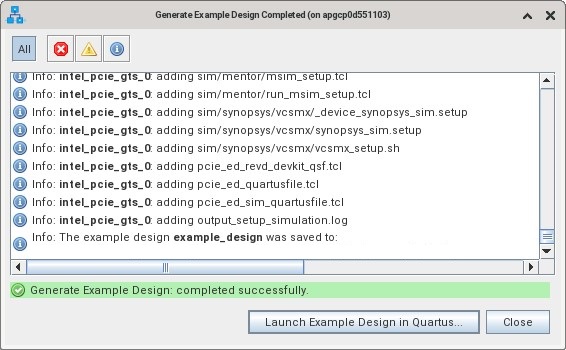

- After the design example generation is completed, click Launch Example Design in Quartus® Prime.

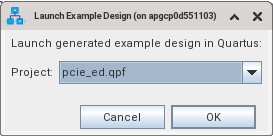

- Select pcie_ed.qpf and click OK to open the newly generated design example in the Quartus® Prime Pro Edition software.

- In the Quartus® Prime Pro Edition software, click Processing → Start Compilation to compile the design example and generate the bitstream (.sof) file.

Note: Design example compilation is not supported when you enable the Enable PIPE Mode Simulation parameter setting in the System Settings tab of the IP Parameter Editor GUI. PIPE mode simulation for the design example is supported by default as the Enable PIPE Mode Simulation parameter setting in the Example Designs tab of the IP Parameter Editor GUI is enabled by default.

- Examine the design compilation results like resource utilization and timing result.

- Close your design example project.