GTS Transceiver PHY User Guide: Agilex™ 5 FPGAs and SoCs

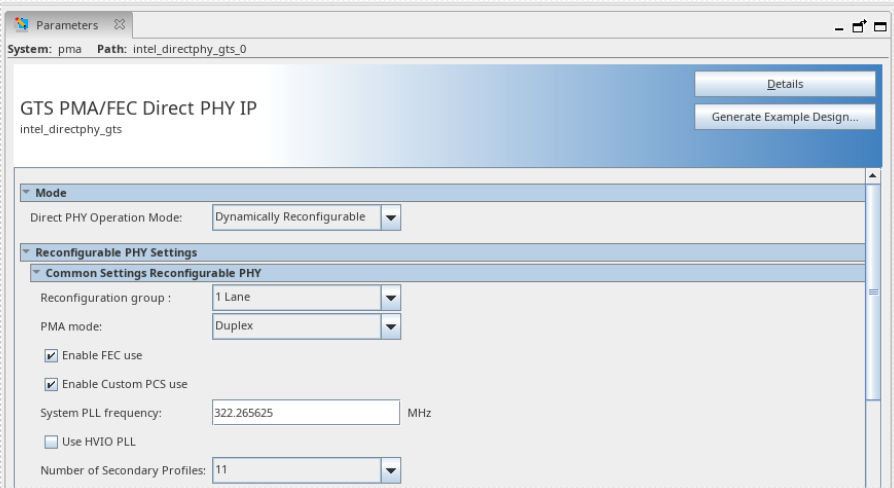

3.3.3. Dynamically Reconfigurable PHY Settings

When you generate the GTS PMA/FEC Direct PHY IP in the Dynamically Reconfigurable PHY mode, you cannot directly instantiate it into your design in the Quartus® Prime Pro Edition software. Refer to the additional steps outlined in the GTS Dynamic Reconfiguration Controller IP User Guide and the GTS PMA/FEC Direct PHY IP Dynamically Reconfigurable PHY Example Design section of this document.

| Parameter | Values | Description |

|---|---|---|

| Reconfigurable group | 1 lane 2 lanes 4 lanes |

Sets reconfiguration group by selecting number of lanes that needs to be reconfigured. Only 1, 2, and 4 lanes are supported in the current Quartus® Prime Pro Edition software release. Default value is 1 lane. In the Quartus® Prime 25.3 release, Dynamic Reconfiguration (DR) is only supported between profiles with the same number of lanes within the group. DR between profiles with different lane counts is not supported. |

| PMA mode | Duplex, TX Simplex, RX Simplex |

Selects the transceiver operation mode. Default value is Duplex |

| Enable FEC use | On/Off | Enables the FEC option for all reconfigurable DPHY profiles. When this option is enabled, FEC for each profile can be individually enabled or disabled in the FEC tab and configured with the required FEC option for that specific profile. Default value is Off |

| Enable Custom PCS use | On/Off | Enables the MII/64/66 Interface (Media-Independent Interface) with PCS enabled. Default value is Off.

Note: When you select the Dynamically Reconfigurable setting for the Direct PHY Operation Mode parameter, the Enable Custom PCS mode only supports the IEEE MII Interface custom PCS interface.

|

| System PLL Frequency | 32.5 to 1000 MHz | Specifies the system PLL clock frequency (MHz) and is applicable if Datapath clocking mode is selected as system PLL. Default value is 322.265625 MHz

Note: You must ensure that the system PLL frequency and GTS System PLL Clocks IP frequency is set to the same value if you are using the system PLL clocking mode.

|

| Use HVIO PLL | On/Off | Enables the use of the HVIO bank's IOPLL in place of the system PLL.

Note: This feature is currently only enabled for single-bank devices, and does not support the PCS/FEC Direct mode yet.

|

| Number of Secondary profiles | 1 - 11 | Specifies the total number of secondary profiles. Default value is 1. |