GTS Transceiver PHY User Guide: Agilex™ 5 FPGAs and SoCs

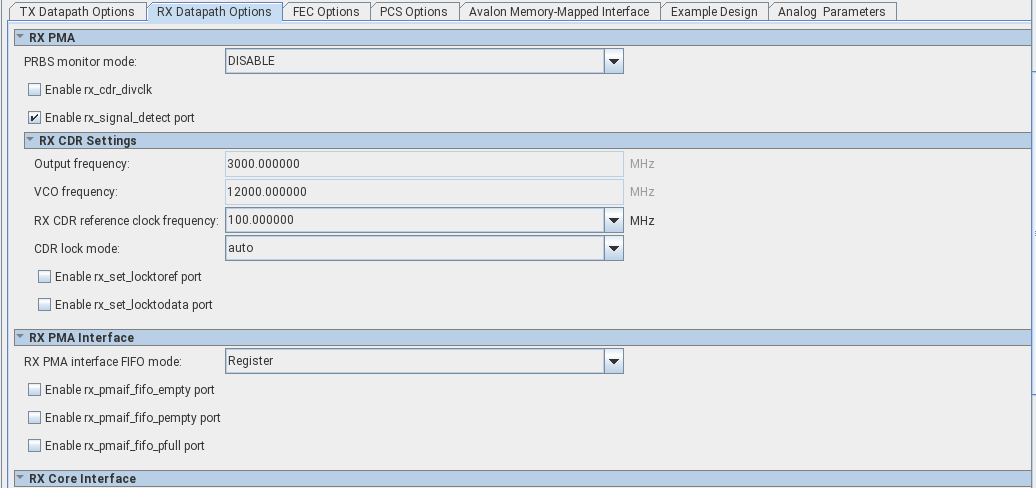

3.3.5. RX Datapath Options

| Parameter | Values | Description |

|---|---|---|

| RX PMA Parameters | ||

| PRBS monitor mode | disable, PRBS7, PRBS9, PRBS10, PRBS13, PRBS15, PRBS23, PRBS31 |

Enables hard PRBS verifier with the PRBS polynomial selection. Default value is disable. |

Enable rx_cdr_divclk |

On/Off | Enables the port representing RX CDR clock output from RX PMA to the local reference clock pin (set as output) or the CDR clock output pin. The physical port is typically used for CPRI. Default value is Off. |

| Enable rx_signal_detect port | On/Off | Enables the rx_signal_detect port. This port is used for protocols such as SATA and SAS for out-of-band (OOB) signal detection. Default value is Off. |

| RX CDR Settings | ||

| Output frequency | Output | Specifies the non editable RX CDR output frequency initial value derived from the IP configuration. |

| VCO frequency | Output | Specifies the non editable RX CDR VCO frequency initial value derived from the IP configuration. |

| RX CDR reference clock frequency | 25 to 380 MHz | Selects the reference clock frequency (MHz) for CDR. Default value is 156.25 MHz. |

| CDR lock mode | auto manual |

When auto is selected, during user initiated reset or power-up, CDR first tries to lock to reference and then locks to data if present. By default, loss of lock to data re-triggers reset RX PMA reset. When manual is selected, you must drive i_rx_set_locktoref to control the CDR lock behavior. If i_rx_set_locktoref is low CDR operates in auto mode, and in lock to reference mode if it is high. When Enable rx_cdr_divclk is enabled, only auto mode is available. Default value is auto. |

| Enable rx_set_locktoref port | On/Off | This parameter is valid only when CDR lock mode is set to manual lock to reference. This signal only takes effect when adaptation is set to manual mode. Asserting this signal keeps CDR in lock to reference mode. Deasserting this signal keeps CDR in auto mode. When switching modes, assert reset. In manual mode, you must notify the reset controller to ignore lock-to-data status by setting the soft CSR register 0x818[0] to 1'b1. Default value is Off. For better jitter performance in Manual Lock to Reference mode, you are recommended to read-modify-write (RMW) the register RX CDR VCO Reference Proportional Nominal Gain Value 0x091580[15:12] to 0xF. This is required for every RX CDR used in this mode. You need to control the correct offset address of each RX CDR lane and RMW to the correct RX CDR channel. |

| Enable rx_set_locktodata port | On/Off | You can only enable this port when the CDR lock mode is set to manual lock-to-reference. This signal only takes effect when Adaptation mode is set to manual. Enable_rx_set_locktoref port is asserted, and CDR is in manual mode. Asserting this signal keeps CDR in manual lock-to-data mode. Deasserting this signal keeps CDR in manual lock-to-reference mode, which is used for oversampling applications. Default value is Off.

Note: This is a preliminary feature.

|

| Enable rx_cdr_fast_freeze_sel port | On/Off | This port is used for GPON. When the PMA configuration rules parameter is set to GPON, you must enable and tie the i_rx_cdr_fast_freeze_sel signal to 1'b0. It ensures that the i_rx_cdr_freeze signal propagates correctly. Default value is Off. |

| Enable rx_cdr_freeze port | On/Off | This port is used for GPON. When the PMA configuration rules parameter is set to GPON, you must enable and drive the i_rx_cdr_freeze signal to freeze the CDR lock state during non-active time slots. Default value is Off |