F-Tile Ethernet Intel® FPGA Hard IP Design Example User Guide

ID

683804

Date

4/01/2024

Public

A newer version of this document is available. Customers should click here to go to the newest version.

1. Quick Start Guide

2. Design Example: Single IP Core Instantiation

3. Design Example: Single IP Core Instantiation with Precision Time Protocol

4. Design Example: Single IP Core Instantiation with Auto-Negotiation and Link Training

5. Design Example: Multiple IP Core Instantiation

6. Design Example: Two Separate Instances of Auto-Negotiation and Link Training and Ethernet IP Design

7. F-Tile Ethernet Intel® FPGA Hard IP Design Example User Guide Archives

8. Document Revision History for the F-Tile Ethernet Intel FPGA Hard IP Design Example User Guide

1.1.3. Generating Multiple IP Instance Design

Figure 5. Procedure

- In the Quartus® Prime Pro Edition, click File > New Project Wizard to create a new Quartus® Prime project, or File > Open Project to open an existing Quartus® Prime project. The wizard prompts you to specify a device.

- Specify the device family Agilex 7 (F-Series/I-Series) and select device with F-tile for your design.

- Select Tools > IP Catalog to open the IP Catalog and select F-Tile Ethernet Intel FPGA Hard IP.

- Specify a top-level name <your_ip> and the folder for your custom IP variation. The parameter editor saves the IP variation settings in a file named <your_ip> .ip.

- Click Create. The IP parameter editor appears.

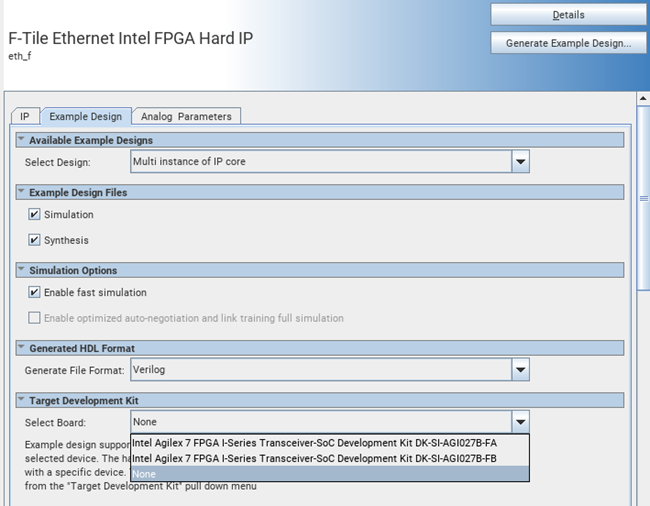

Figure 6. Example Design Tab

- Specify the parameters in the IP tab. For exact IP parameter setting, refer to the Selected IP Parameter Settings table in the desired Design Example chapter.

- Specify the parameters in the Example Design tab.

| Parameters | Value | Description |

|---|---|---|

| Select Design | Multi Instance of IP Core |

Selects the multiple instance of IP core for example design. |

| Example Design Files | Simulation Synthesis |

Simulation option generates the testbench and compilation-only project. Synthesis option generates the hardware design example. |

| Simulation Options | Enable fast Simulation Enable Optimized Auto-Negotiation and Link Training full simulation |

Enables the fast simulation in AN/LT IP. Enable Optimized Auto-Negotiatin and Link Training full simulation option enables the optimized simulation for full auto-negotiation and link training flow in generated example design. This option cannot be enabled along with Enable Fast Simulation. |

| Generated File Format | Verilog VHDL |

Select the HDL files format. If you select VHDL, you must simulate the testbench with a mixed-language simulator. |

| Target Development Kit | None Agilex™ 7 I-Series Transceiver-SoC Development Kit DK-SI-AGI027FA Agilex™ 7 I-Series Transceiver-SoC Development Kit DK-SI-AGI027FB |

Target development kit option specifies the target development kit used to generate the project. |

- Click the Generate Example Design button.

The software generates all design files in sub-directories. You require these files to run simulation, compilation, and hardware testing.

Related Information