1.4.1. Tutorial Design Files

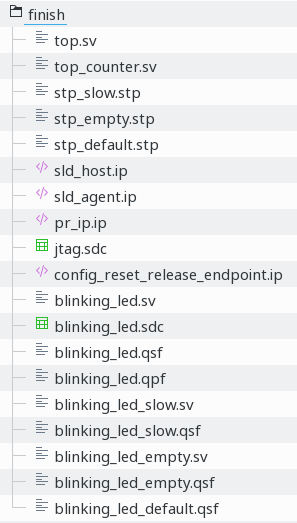

The design folder contains two subfolders: The start folder contains the files that you need to follow this tutorial, and the finish folder contains the complete set of files you create using this application note. Reference these files at any point during the walkthrough.

| File Name | Description |

|---|---|

| top.sv | Top-level file. Contains the flat implementation of the design. This module instantiates the blinking_led sub-partition and the top_counter module. This module also instantiates the SLD JTAG Bridge Agent for debugging purposes. |

| top_counter.sv | Top-level 32-bit counter that controls LED[1] directly. The registered output of the counter controls LED[0], and powers LED[2] and LED[3] via the blinking_led module. |

| blinking_led.sdc | Defines the timing constraints for the project. |

| blinking_led.sv | This module acts as the PR partition. The module receives the registered output of top_counter module, which controls LED[2] and LED[3].This module also instantiates the SLD JTAG Bridge Host and the Intel Configuration Reset Release Endpoint to Debug Logic IP for debugging the default persona. |

| blinking_led.qpf | Intel® Quartus® Prime project file that contains a list of all the revisions in the project. |

| blinking_led.qsf | Intel® Quartus® Prime settings file that contains assignments and settings for the base revision of the project. |

| blinking_led_default.qsf | Contains assignments and settings for the blinking_led_default implementation revision of the project. |

| blinking_led_slow.qsf | Contains assignments and settings for the blinking_led_slow implementation revision of the project. |

| blinking_led_empty.qsf | Contains assignments and settings for the blinking led empty of the project. |

| blinking_led_slow.sv | Slower version of the PR logic. On this version, the led blinks at a slower rate than the default PR persona. The module receives the registered output of top_counter module, which controls LED[2]and LED[3]. This module also instantiates the SLD JTAG Bridge Host and the Intel Configuration Reset Release Endpoint to Debug Logic IP for debugging this persona. |

| blinking_led_empty.sv | Empty version of the PR logic. This module holds the outputs at a constant. The module receives the registered output of top_counter module, which controls LED[2] and LED[3]. This module also instantiates the SLD JTAG Bridge Host and the Intel Configuration Reset Release Endpoint to Debug Logic IP for debugging this persona. |

| pr_ip.ip | Intel® Arria® 10 Partial Reconfiguration Controller IP. This Intel® FPGA IP enables PR over a JTAG connection. |

The following Figure shows the list of files in the finish folder: