Answers to Top FAQs

1. Overview of the Power and Thermal Calculator

2. Estimating Power Consumption with the Power and Thermal Calculator

3. Power and Thermal Calculator Graphical User Interface

4. Power and Thermal Calculator Pages

5. Factors Affecting the Accuracy of the PTC

6. Power and Thermal Calculator User Guide Archive

7. Document Revision History for the Power and Thermal Calculator User Guide

A. Measuring Static Power

4.1. PTC - Power Summary/Navigation

4.2. PTC - Common Page Elements

4.3. PTC - Main Page

4.4. PTC - Logic Page

4.5. PTC - RAM Page

4.6. PTC - DSP Page

4.7. PTC - Clock Page

4.8. PTC - PLL Page

4.9. PTC - I/O Page

4.10. PTC - Transceiver Page

4.11. PTC - HPS Page

4.12. PTC - Crypto Page

4.13. PTC - NOC Page

4.14. PTC - HBM Page

4.15. PTC - Thermal Page

4.16. PTC - Report Page

4.8. PTC - PLL Page

Each row in the PLL data entry page of the Power and Thermal Calculator (PTC) represents one or more PLLs in the device.

Supported PLL types are family dependent, as outlined in the PLL Page Information table:

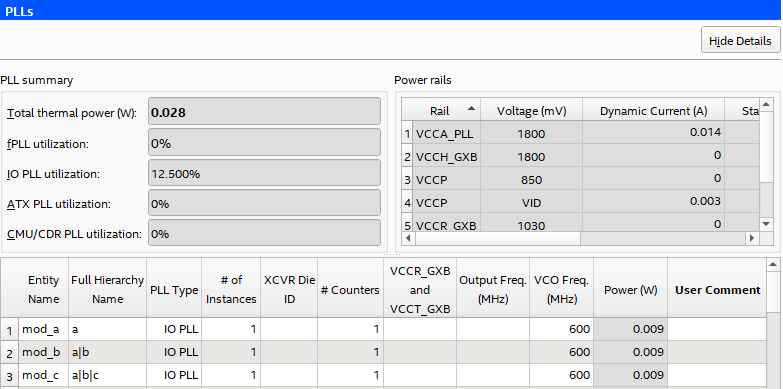

Figure 41. PLL Page

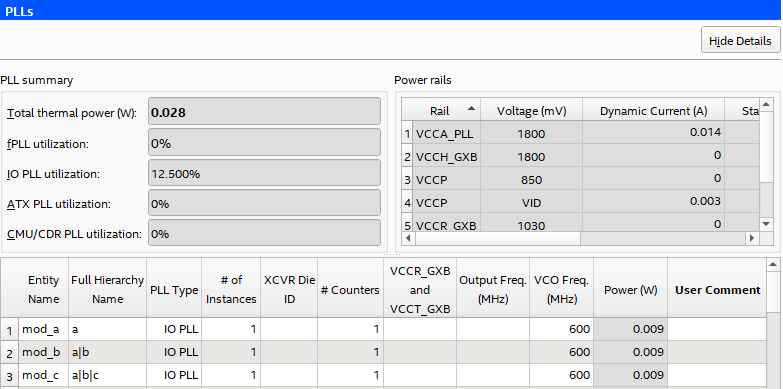

Figure 42. PLL Page ( Agilex™ FPGA Portfolio Devices)

| Column Header | Description |

|---|---|

| Total thermal power (W) | Reports the total thermal power (in W). |

| fPLL utilization | Reports the percentage of fPLL utilization. (This field is available for Stratix® 10 devices only.) |

| IO PLL utilization | Reports the percentage of I/O PLL utilization. |

| ATX PLL utilization | Reports the percentage of ATX PLL utilization. (This field is available for Stratix® 10 devices only.) |

| CMU/CDR PLL utilization | Reports the percentage of CMU/CDR PLL utilization. (This field is available for Stratix® 10 devices only.) |

| Power rails | Indicated the voltage (mV), dynamic current (A), and standby current (A), for various power rails. |

| Column Heading | Description |

|---|---|

| Entity Name | Specify a name for the PLL entity in this column. This is an optional value. |

| Full Hierarchy Name | Specify the hierarchical path relevant to this entry. This is an optional entry. When entering levels of hierarchy, the pipe character (|) denotes a level of hierarchy. |

| PLL Type | Specifies the type of PLL, which may include the following:

|

| # of Instances | The number of logical PLL instances with this type, counter, voltage, and frequency combination. |

| Bank ID | The I/O bank ID for this row. A bank location can be assigned to PLLs to change how the PLLs are placed, affecting thermals and utilization. (This column is available for Agilex™ FPGA portfolio devices only.) |

| # PLL Blocks | Enter the number of PLL blocks with the same combination of parameters. |

| XCVR Die ID | Specify the transceiver die on which PLLs on this row are located. This field is not applicable for I/O PLLs, nor fabric-feeding I/O PLLs. |

| # Counters | Enter the number of counters of the PLL. |

| VCCR_GXB and VCCT_GXB Voltage | Specify the voltage of the VCCR_GXB and VCCT_GXB rails. This field is not applicable for I/O PLLs, nor fabric-feeding I/O PLLs. |

| Output Freq (MHz) | Specify the output frequency for CMU and ATX PLLs. |

| VCO Freq (MHz) | Specify the internal VCO operating frequency for PLLs. |

| Total Power (W) | Shows the total estimated power for this row (in W). |

| User Comments | Enter any comments. This is an optional entry. |

For more information about the PLLs available in Agilex™ FPGA portfolio devices, refer to the Clocking and PLL User Guide: Agilex™ 3 FPGAs and SoCs, Agilex™ 5 Clocking and PLL User Guide and Agilex™ 7 Clocking and PLL User Guide.