28.14.1. Block Diagram

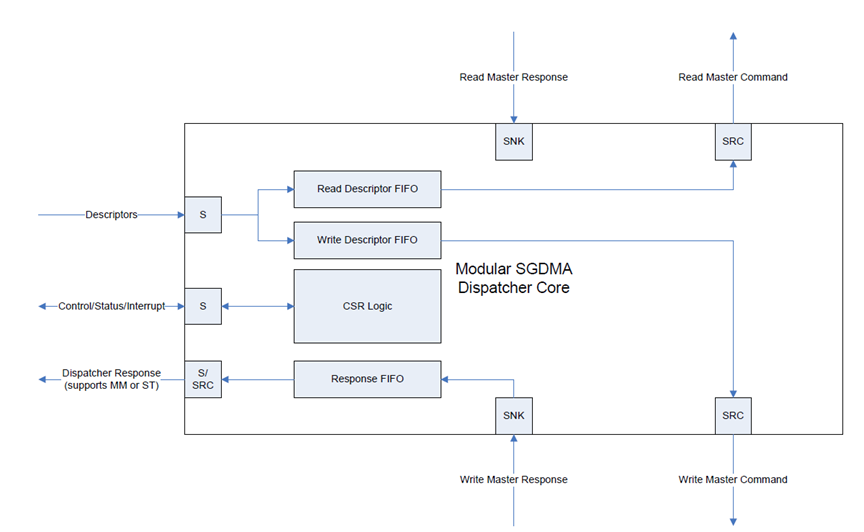

The following figure shows the significant blocks that make up the mSGDMA Dispatcher IP.

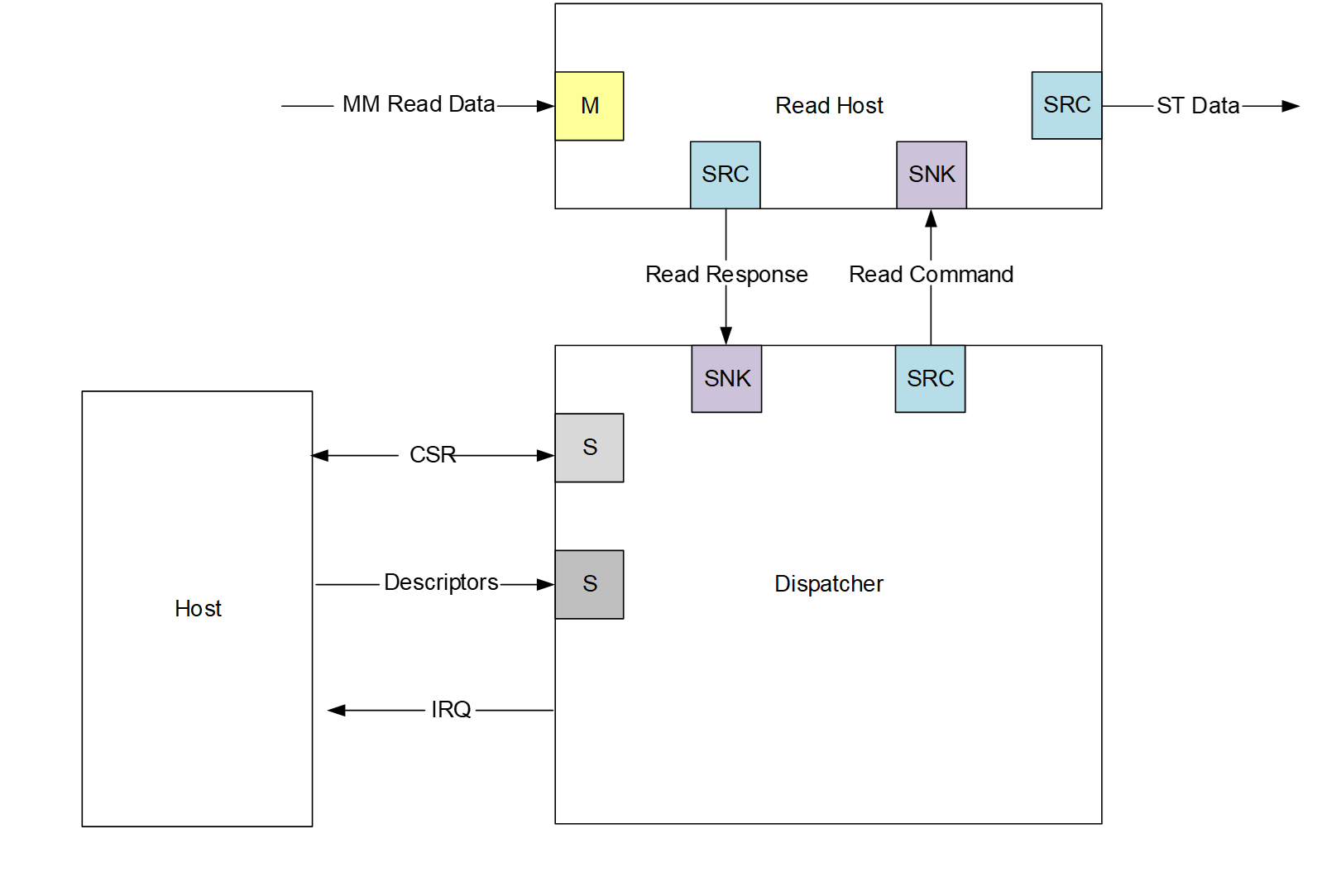

When the modular SGDMA is configured for Memory-Mapped to Streaming, the write master command port and write master response port are not exposed.

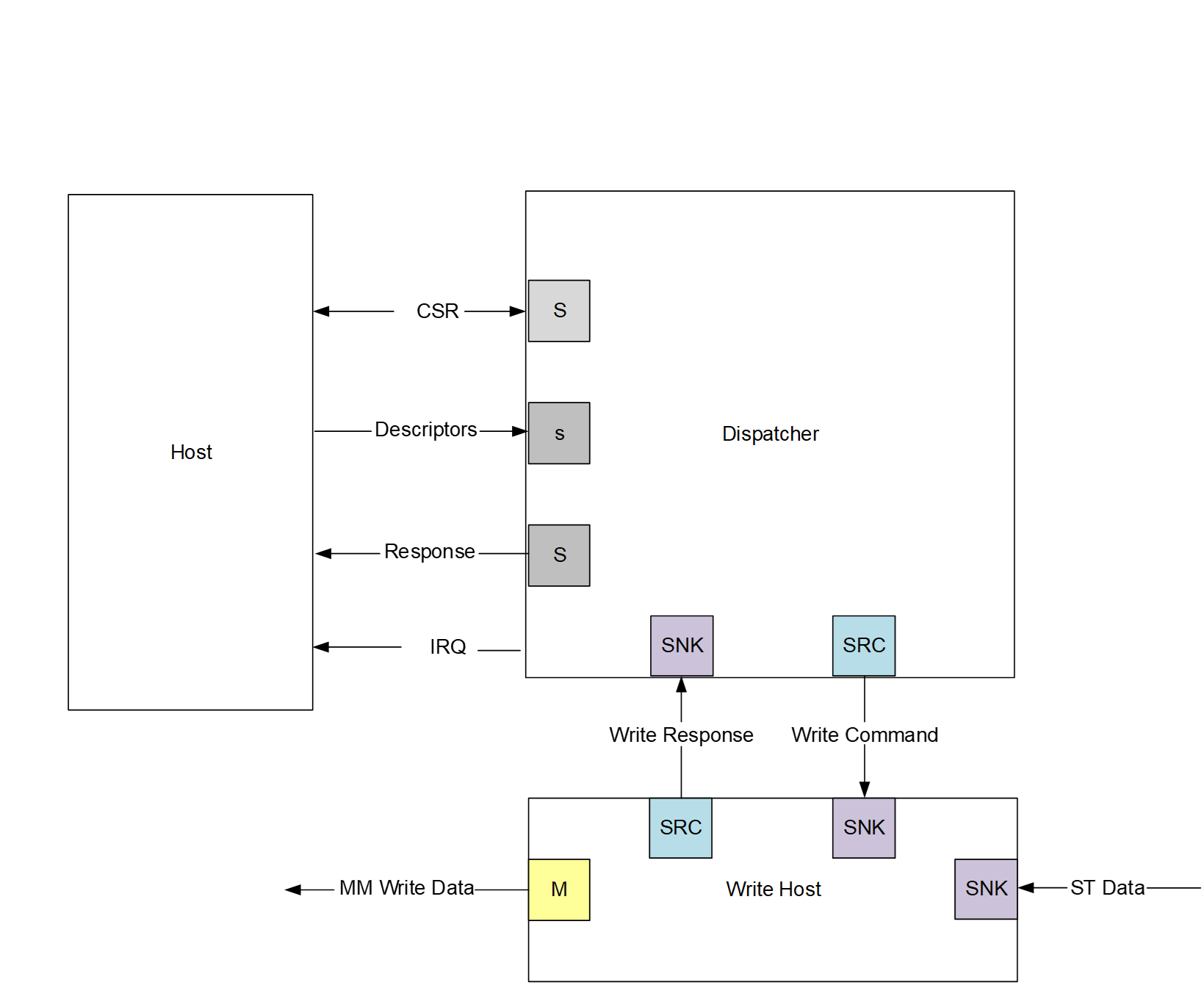

When the modular SGDMA is configured for Streaming to Memory-Mapped, the read master command port and read master response port are not exposed.

The dispatcher memory-mapped response agent port is only used for streaming to memory-mapped transfers to communicate response information such as actual bytes transferred, early termination and errors back to the host upon completion of each descriptor execution. Similiarly, the response port can be configured to be a streaming source port. However, streaming response source port is not applicable for Memory-Mapped to Streaming configuration if the descriptor pre-fetching module is absent.

The dispatcher response port is necessary if a SGDMA descriptor pre-fetching module is added to the modular architecture. In this case, the response port should be configured to be a streaming source port and it supports for all transfer types: Memory-Mapped to Memory-Mapped, Memory-Mapped to Streaming or Streaming to Memory-Mapped configurations.

Refer to Response Port section for more details on memory-mapped response agent or streaming response source interface.

In addition, the dispatcher IP has one Avalon® Memory-Mapped CSR agent interface for the host processor to access the configuration register in the dispatcher IP.

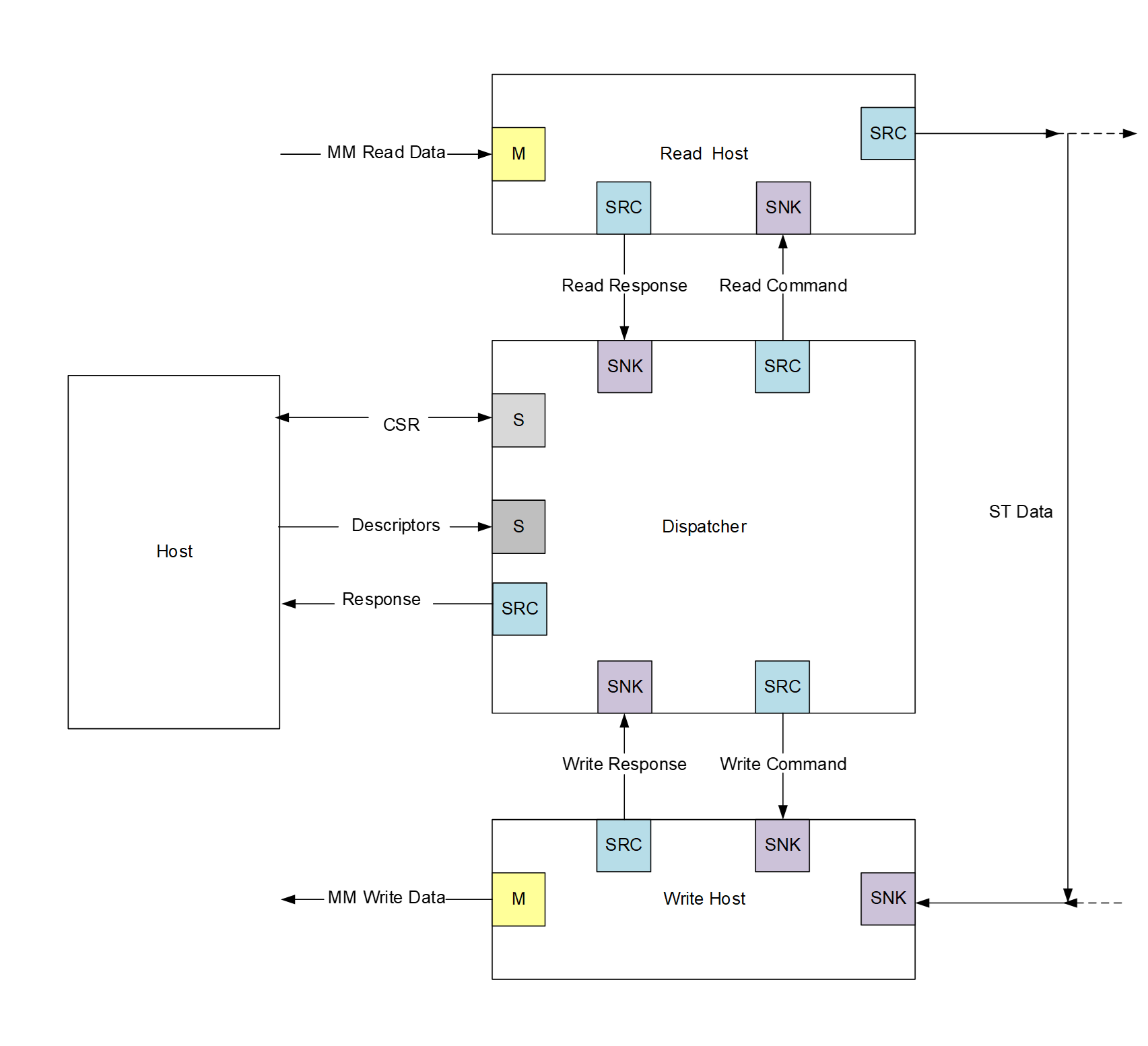

The following figures illustrate mSGDMA IP which consists of dispatcher, read master and/or write master micro core for the three main modular SGDMA configurations that suit the needs for most system designers as shown below. The dispatcher, read master and write master micro core of the mSGDMA are instantiated automatically according to the structure configured for the mSGDMA use model.