仅对英特尔可见 — GUID: mwh1410384625824

Ixiasoft

1. 系统调试工具概述

2. 使用Signal Tap逻辑分析仪进行设计调试

3. Quick Design Verification with Signal Probe

4. 使用外部逻辑分析器进行在系统调试(In-System Debugging Using External Logic Analyzers)

5. 存储器和常量的在系统修改(In-System Modification of Memory and Constants)

6. 使用In-System Sources and Probes进行设计调试

7. 使用System Console分析和调试设计

8. 调试收发器链路

9. Intel® Quartus® Prime Pro Edition用户指南调试工具存档

A. Intel® Quartus® Prime Pro Edition用户指南

2.1. Signal Tap逻辑分析仪

2.2. Signal Tap Logic Analyzer任务流程概述

2.3. 配置Signal Tap Logic Analyzer

2.4. 定义触发器

2.5. 编译设计

2.6. 对目标器件或者器件编程

2.7. 运行Signal Tap Logic Analyzer

2.8. 查看,分析和使用采集的数据

2.9. 使用Signal Tap Logic Analyzer调试部分重配置设计

2.10. 使用Signal Tap Logic Analyzer调试基于模块的设计

2.11. 其他功能

2.12. 设计实例:使用Signal Tap Logic Analyzers

2.13. 自定义触发流程应用示例

2.14. Signal Tap脚本支持

2.15. 使用Signal Tap Logic Analyzer进行设计调试修订历史

7.1. System Console简介

7.2. System Console调试流程

7.3. 与System Console交互的IP内核

7.4. 启动System Console

7.5. System Console GUI

7.6. System Console命令

7.7. 在命令行模式下运行System Console

7.8. System Console服务

7.9. System Console示例和教程

7.10. 板载 Intel® FPGA Download Cable II支持

7.11. 系统验证流程中的MATLAB*和Simulink*

7.12. 不推荐使用的命令

7.13. 使用System Console分析和调试设计修订历史

仅对英特尔可见 — GUID: mwh1410384625824

Ixiasoft

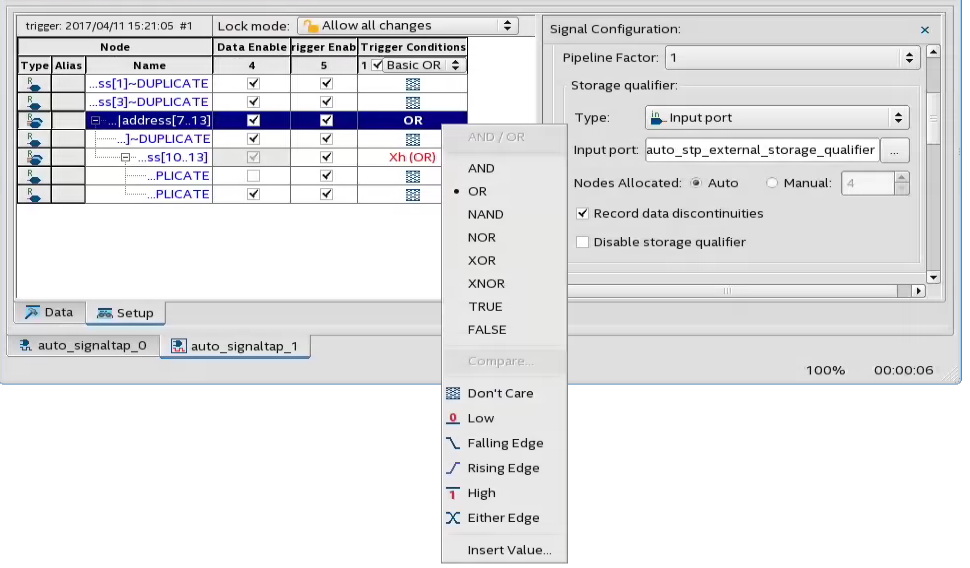

2.4.1.1. 使用Basic OR触发条件和嵌套组

当使用Basic OR触发类型将一组信号指定为嵌套组(组中组)时,Signal Tap Logic Analyzer 会生成一个高级触发条件。此条件会在组内对信号进行分类,以最大程度地减少重新编译设计的需求。 只要节点的父子(parent-child)关系保持恒定,高级触发条件就不会改变。您可以修改节点的同级关系,而无需重新编译设计。

嵌套触发条件的评估优先级从具有叶组的底层开始。Logic Analyzer使用结果逻辑值来计算父组的逻辑值。如果手动设置组的值,那么组成员的逻辑值不会影响组触发的结果。创建嵌套的触发条件:

- 在Trigger Conditions下选择Basic OR。

- 在Setup选项卡中,选择几个节点。在您的选择中包括组。

- 右键单击Setup选项卡,然后选择Group。

- 选择嵌套的组,然后右键单击以设置一个组触发条件,应用AND,OR,NAND,NOR,XOR,XNOR或者 logical TRUE or FALSE。

注: 对底层组(没有组作为子组的组)只能选择OR和AND组触发条件。图 30. 将触发条件应用于嵌套组