A newer version of this document is available. Customers should click here to go to the newest version.

10.4. Instantiating the FPGA AI Suite IP in Platform Designer

Use Platform Designer to instantiate or integrate the FPGA AI Suite IP in your FPGA design. The FPGA AI Suite compiler produces an IP index file (.ipx) file that you can use to add the design in Platform Designer. For more information about IP component description files like an IP index file, refer to "IP Component Description Files" in Quartus® Prime Pro Edition User Guide: Platform Designer .

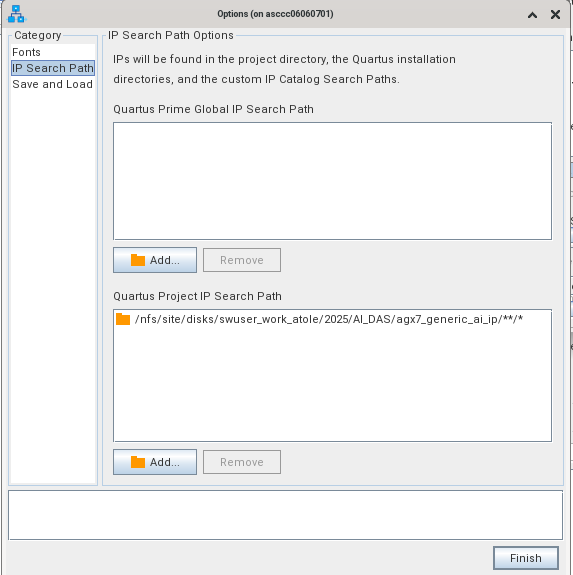

For Platform Designer IP catalog to show the FPGA AI Suite IP, add the location of the .ipx file for the IP to search path for your project as shown in the following image.

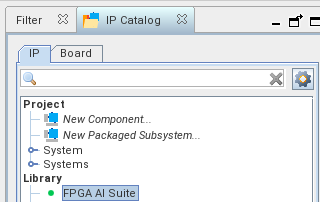

After you update the IP search path, the Platform Designer IP catalog refreshes to show the FPGA AI Suite IP as shown in the image that follows. . For more information about the IP search path in Platform designer, refer to to "IP Search Path Recursive Search" in Quartus® Prime Pro Edition User Guide: Platform Designer .

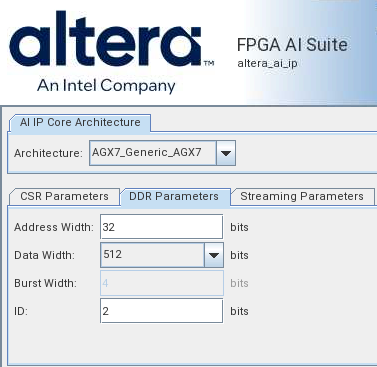

dla_create_ip --flow create_ip \ --arch=$COREDLA_ROOT/example_architectures/AGX7_Generic.arch \ --overwrite \ --ip_dir ./ip

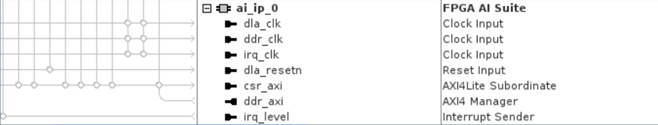

After the IP is instantiated as shown in the following image, connect your IP to the exposed signals.