GTS Dynamic Reconfiguration Controller IP User Guide: Agilex™ 5 FPGAs and SoCs

ID

849710

Date

10/22/2025

Public

1. Overview

2. Quick Start Guide

3. Configuring and Generating the IP

4. Integrating the GTS Dynamic Reconfiguration Controller IP With Your Application

5. Designing with the IP Core

6. Designing the IP Solution

7. Sharing Clocking and Applying SDC Constraints

8. Runtime Flow

9. Simulating the IP

10. Validating the IP

11. Appendix A: Functional Description

12. Registers

13. Document Revision History for the GTS Dynamic Reconfiguration Controller IP User Guide

3.1. Configuring the Quartus® Prime Pro Edition Project

3.2. Generating Dynamic Reconfiguration Design and Configuration Profiles

3.3. Generating HDL for Synthesis and Simulation

3.4. Using the HSSI Support Logic Assignment Editor

3.5. HSSI Support Logic Generation

3.6. Generating the Design Example

3.7. Compiling the Design Example

9.1. Design Example Features

9.2. Simulating the GTS PMA/FEC Direct PHY Altera FPGA IP Example Design Testbench

9.3. Simulating the Ethernet to CPRI Dynamic Reconfiguration Altera FPGA IP Design Example Testbench

9.4. Simulating the GTS PTP/CPRI Multirate FPGA IP Design Example Testbench

9.5. Simulating the GTS Triple-Speed Ethernet (TSE)/Multirate Ethernet IP Design Example Testbench

10.1. Testing the Hardware Design Example for PMA Direct PHY Multirate

10.2. Testing the Hardware Design Example for Ethernet to CPRI

10.3. Testing the Hardware Design Example for PTP/CPRI Multirate

10.4. Testing the Hardware Design Example for TSE/Multirate Ethernet

10.5. Troubleshooting and Debugging Issues

12.1.1. Register Next ID Configuration 0

12.1.2. Register Next ID Configuration 1

12.1.3. Register Next ID Configuration 2

12.1.4. Register Next ID Configuration 3

12.1.5. Register Next ID Configuration 4

12.1.6. Register Next ID Configuration 5

12.1.7. Register Next ID Configuration 6

12.1.8. Register Next ID Configuration 7

12.1.9. Register Next ID Configuration 8

12.1.10. Register Next ID Configuration 9

12.1.11. Register Next ID Configuration 10

12.1.12. Register Next ID Configuration 11

12.1.13. Register Next ID Configuration 12

12.1.14. Register Next ID Configuration 13

12.1.15. Register Next ID Configuration 14

12.1.16. Register Next ID Configuration 15

12.1.17. Register Next ID Configuration 16

12.1.18. Register Next ID Configuration 17

12.1.19. Register Next ID Configuration 18

12.1.20. Register Next ID Configuration 19

12.1.21. Register Trigger

12.1.22. Register Trigger Status

12.1.23. Register Error Configuration

12.1.24. Register Error Status

3.4.1.3. Properties

You use the Properties pane to set additional properties for items in the DR group list. Selecting an item may reveal more input options in the Properties pane. For DR groups, you select a startup combination from the list of all combinations in the group. For combinations, you designate the combination as the startup combination within its group.

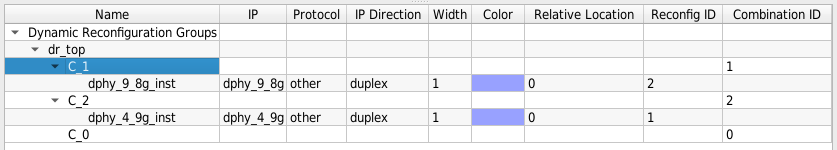

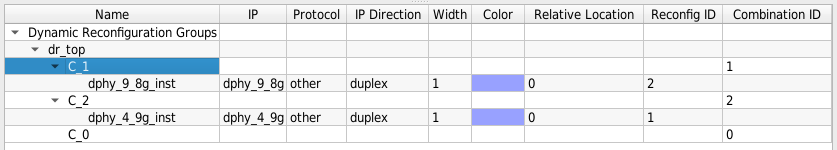

Figure 14. Combination Properties

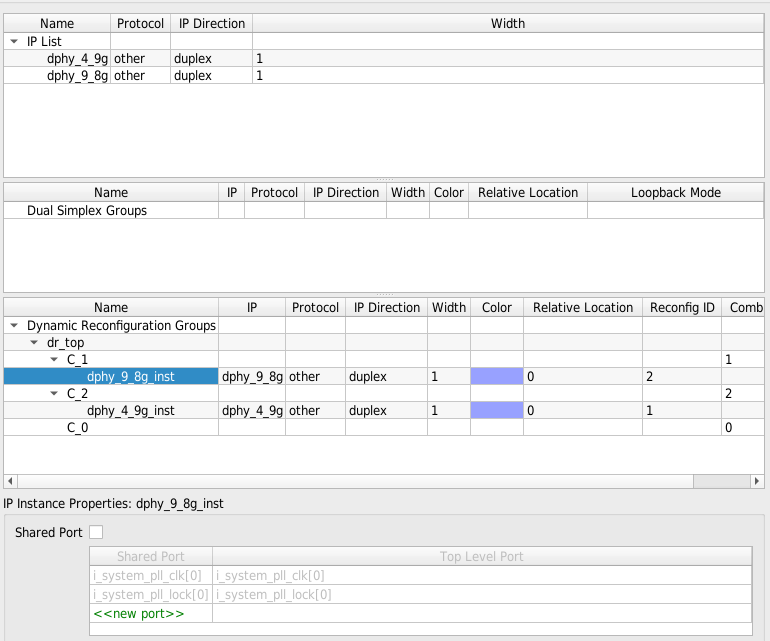

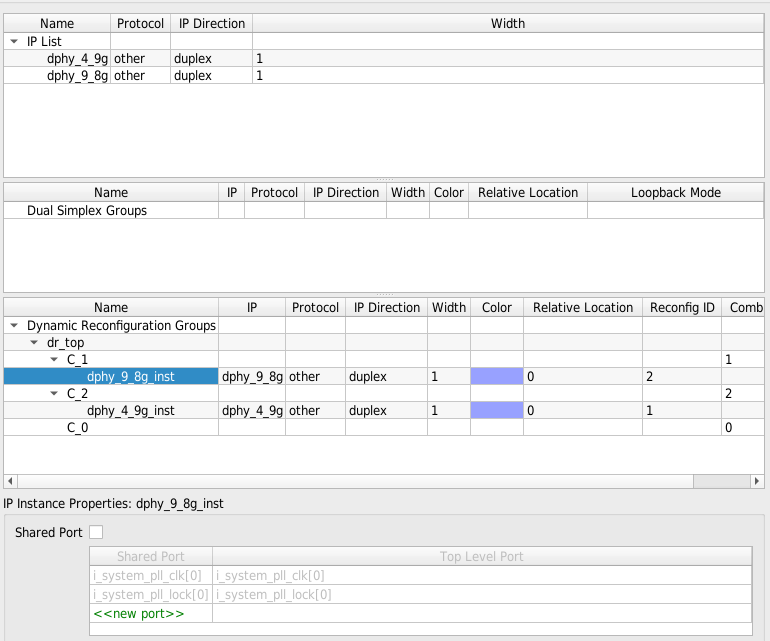

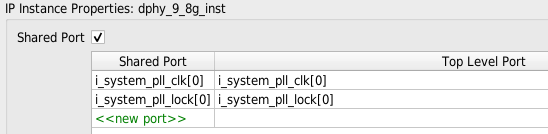

For IP instances, you can choose to share a clock with other instances.

Figure 15. IP Instance Properties

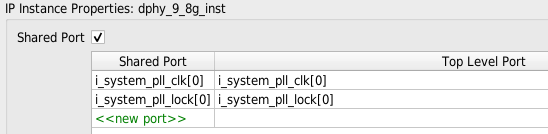

When you check the Shared Port check box, the Shared Ports list and Top Level Port line edit become enabled. You can then select your desired clock port from the list and enter a name for the port in the netlist.

Figure 16. Shared Port Property

| Ethernet | DPHY | CPRI | SDI | MRPHY | TSE | |

|---|---|---|---|---|---|---|

| System PLL | i_clk_sys | i_system_pll_clk | i_syspll_clk | system_pll_clk | i_system_pll_clk | system_pll_clk |

| System PLL Lock | i_syspll_lock | i_system_pll_lock | i_syspll_lock | system_pll_lock | i_system_pll_lock | system_pll_lock |

| Reference Clocks | i_clk_ref_p | i_rx_cdr_refclk_p | i_refclk_rx | rx_cdr_refclk | rx_cdr_refclk_p | rx_cdr_refclk_p |

| i_tx_pll_refclk_p | i_refclk_tx | tx_pll_refclk | tx_pll_refclk_p | tx_pll_refclk_p | ||

| i_refclk_rx_153 | ||||||

| i_refclk_tx_153 | ||||||

| cdr_divclk | o_cdr_divclk | o_rx_cdr_divclk | o_cdr_divclk |