AN 872: Thermal and Power Guidelines: For Intel® Programmable Acceleration Card with Intel® Arria® 10 GX FPGA

3.4. Estimating the Worst Case Core Static Power

Follow these steps to estimate the worst case static power:

- Refer to the Minimal Flow Example to compile a sample AFU located at:

<inteldevstack>/hw/samples/<AFU name>/ - In the Intel® Quartus® Prime Pro Edition software, click File > Open Project and select your .qpf file to open the AFU synthesis project from the following path:

<Acceleration Stack Directory>/hw/samples/<AFU name>/build_synth/build

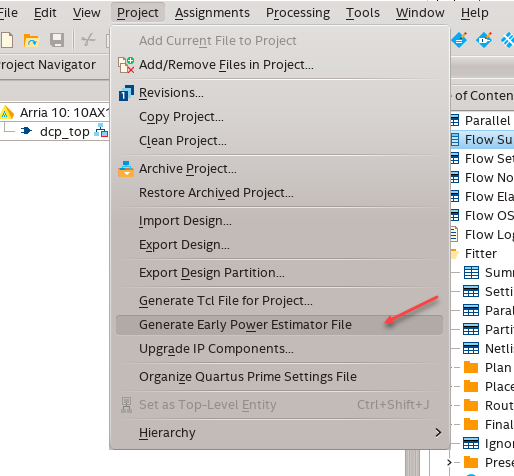

- Click Project > Generate EPE File to create the required .csv file.

Figure 3. Step 2 Illustration

- Open the Early Power Estimator tool5 and click Import CSV icon. Select the above generated .csv file.

Note: You can ignore the warning while importing the .csv file.

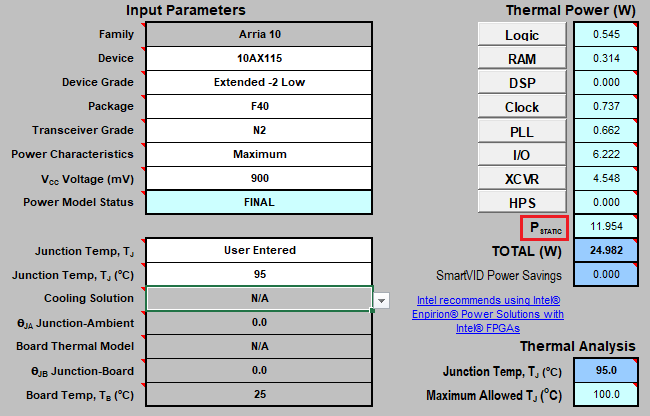

- Inputs parameters are filled out automatically.

- Change the value to User Entered in the Junction Temp. TJ field. And set the Junction Temp. TJ (°C) field to 95

- Change the Power Characteristics field from Typical to Maximum.

- In the EPE Tool, the PSTATIC is the total static power in Watts. You can calculate the worst case core static power from the Report tab

Figure 4. EPE Tool Sample Output

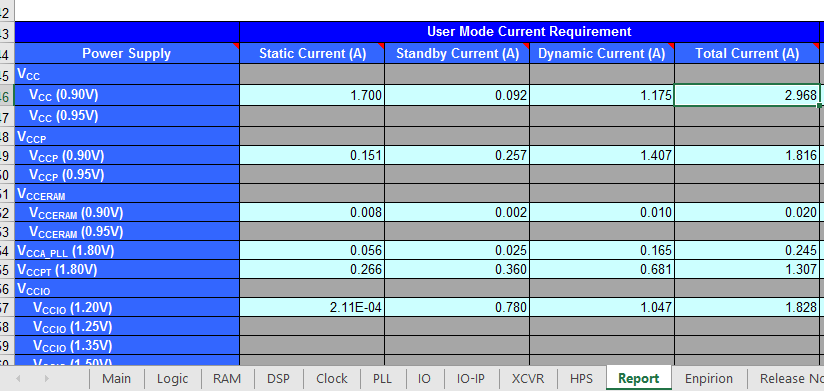

Figure 5. Report Tab

Figure 5. Report Tab

In the example shown above, the total FPGA core static current is the sum of all static current and standby current at 0.9V (VCC, VCCP, VCCERAM).

Enter these value in row Step 3: Worst static power from EPE of the Intel® FPGA PAC Power Estimator Sheet.

Observe the Calculated output row for the maximum power consumption of your AFU.

5 Dowload Information: PowerPlay Early Power Estimator for Intel Arria 10 Devices.