AN 777: Data Word Alignment Calibration With Multiple Intel FPGA PHYLite for Parallel Interfaces IP Cores

ID

683631

Date

1/12/2018

Public

1.1. Features

1.2. Hardware and Software Requirements

1.3. Compiling the Reference Design

1.4. Hardware Setup

1.5. Generating Executable and Linking Format (.elf) Programming File

1.6. Running the Hardware Reference Design

1.7. Results

1.8. Reference Design Architecture

1.9. Document Revision History for AN 777: Data Word Alignment Calibration With Multiple Intel FPGA PHYLite for Parallel Interfaces IP Cores

1.3. Compiling the Reference Design

- Follow the guidelines in Getting Started with the Design Store to download and install the reference design files.

- Open the reference design .qpf file after successfully installing the design templates.

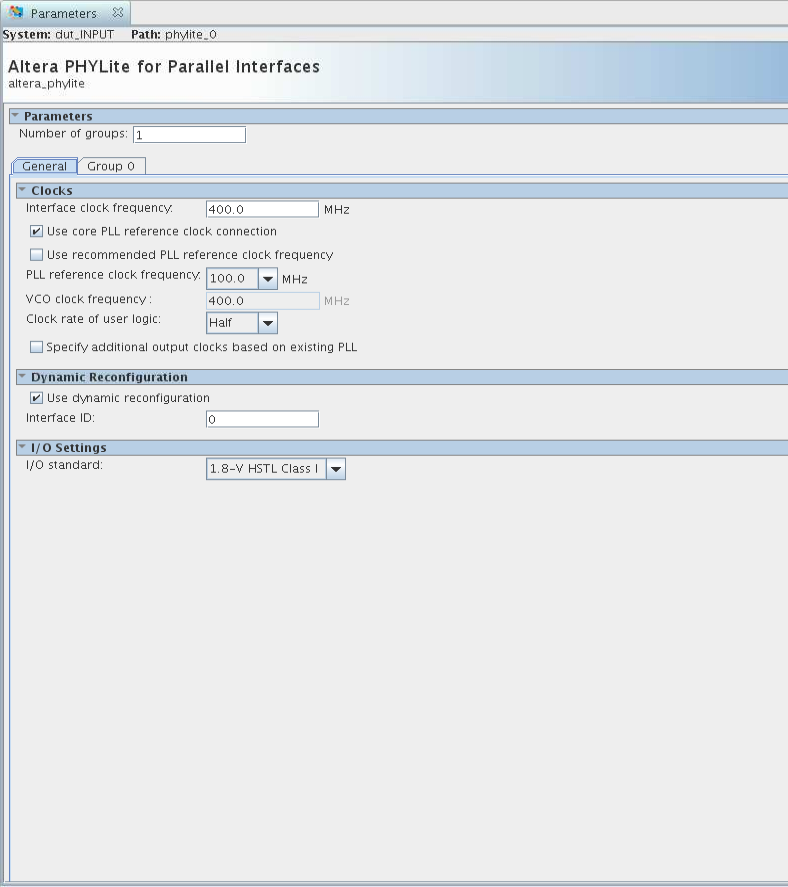

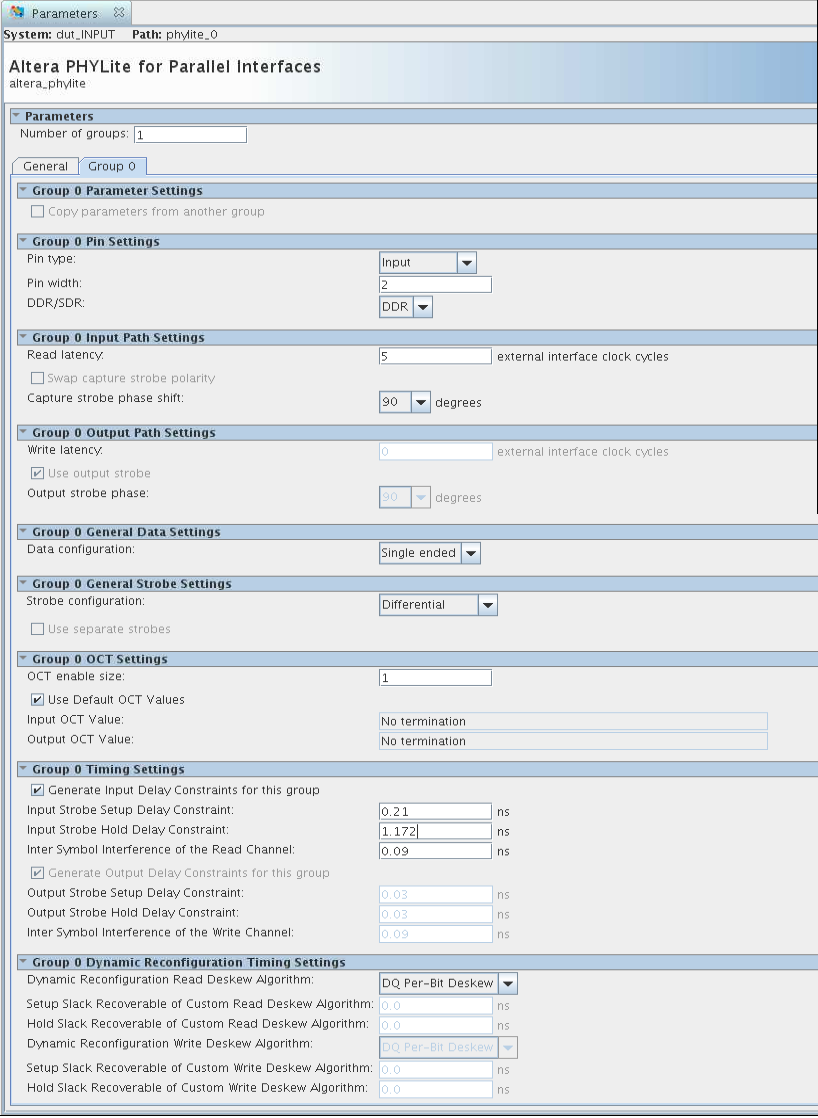

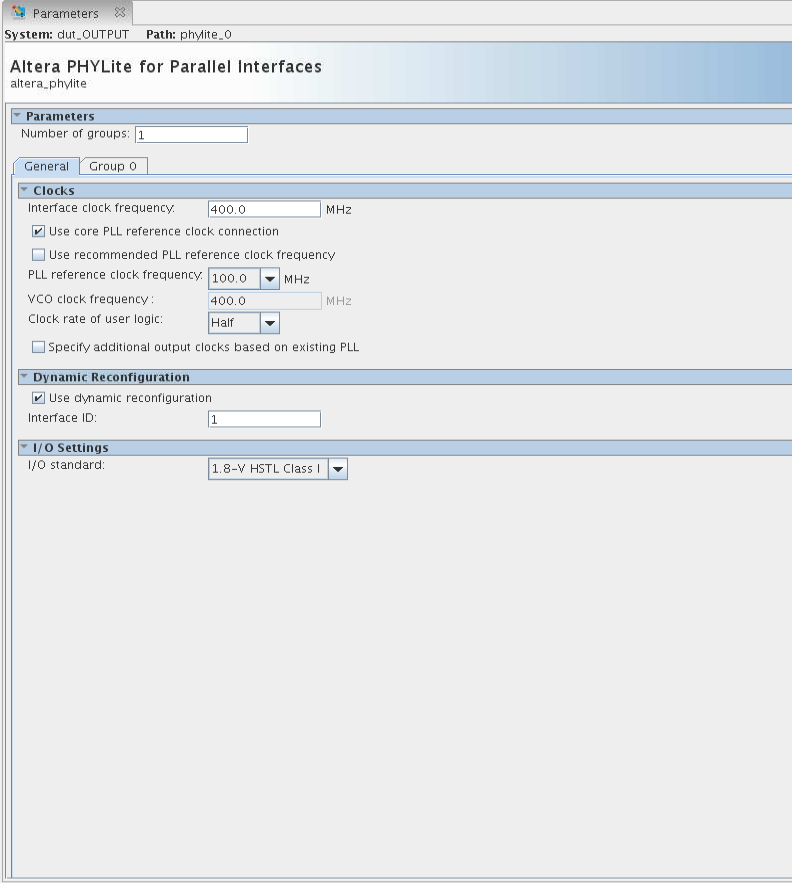

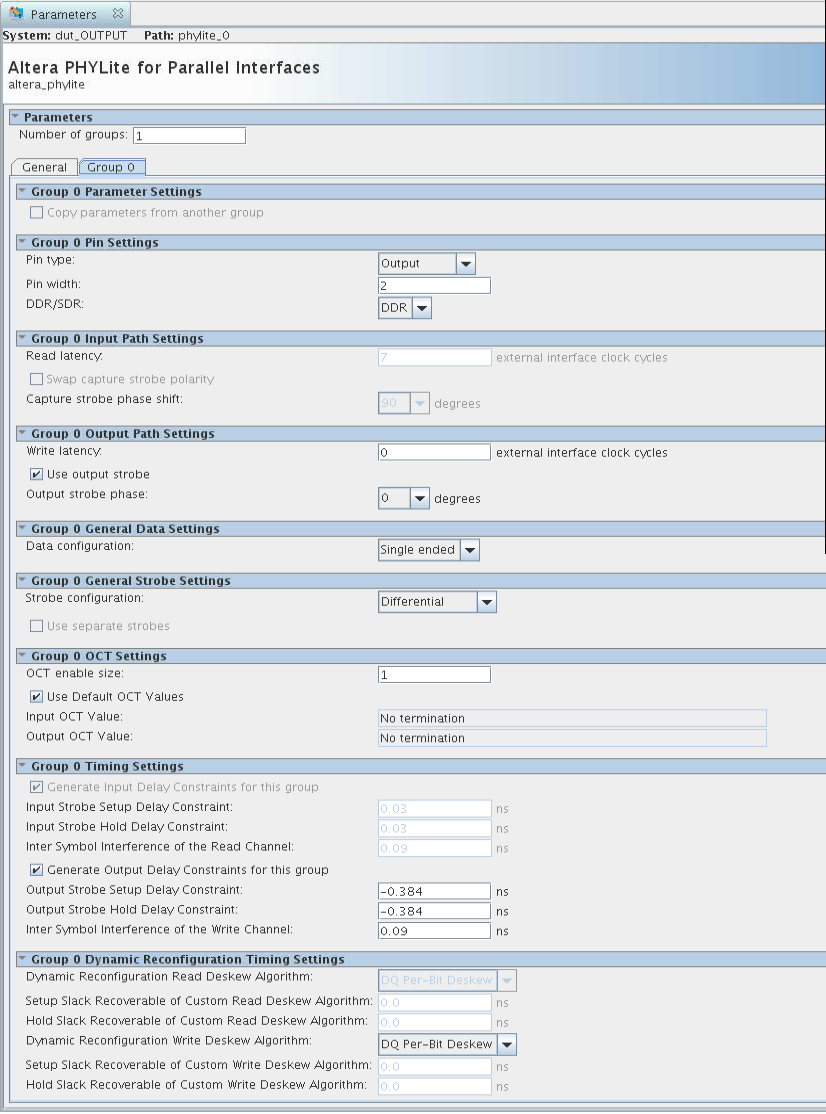

- In the Intel® Quartus® Prime software, open dut_INPUT.qsys and dut_OUTPUT.qsys files. Make sure the Intel FPGA PHYLite IP core has the same configurations shown below:

Figure 1. General Tab Configuration for dut_INPUT Module

Figure 2. Group 0 Tab Configuration for dut_INPUT Module

Figure 2. Group 0 Tab Configuration for dut_INPUT Module Figure 3. General Tab Configuration for dut_OUTPUT Module

Figure 3. General Tab Configuration for dut_OUTPUT Module Figure 4. Group 0 Tab Configuration for dut_OUTPUT Module

Figure 4. Group 0 Tab Configuration for dut_OUTPUT Module

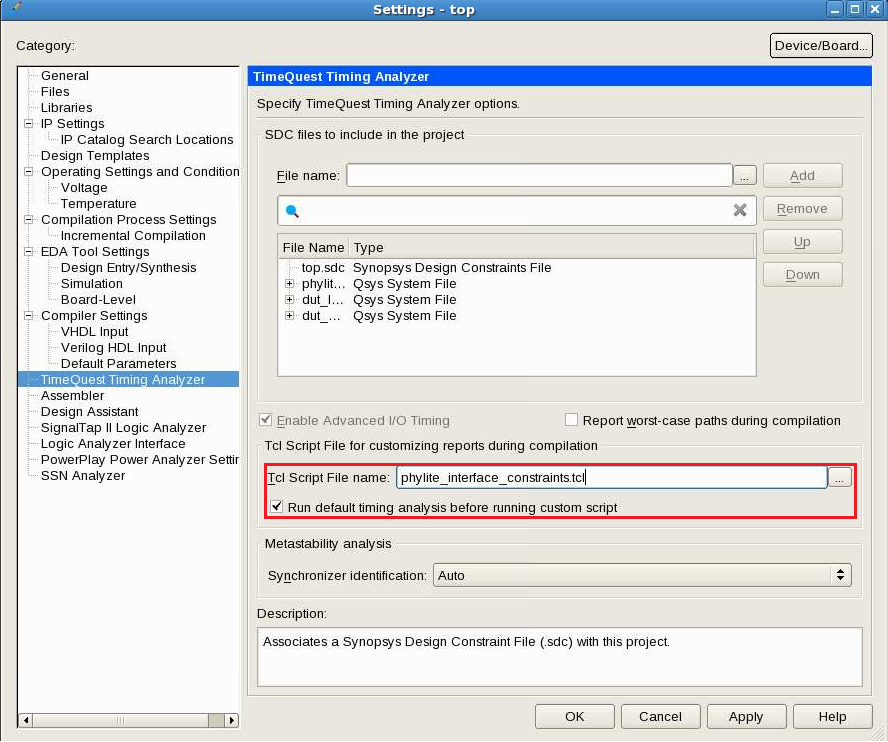

- In Intel® Quartus® Prime software, click on Assignments > Settings > TimeQuest Timing Analyzer.

- In the Tcl Script File name, type in phylite_interface_constraints.tcl and select Run default timing analysis before running customer script.

Figure 5. Adding Interface Constraints Calculation Script

- Click Apply and OK.

- In the Intel® Quartus® Prime, click Processing > Start Compilation to compile the reference design.