Intel® High Level Synthesis Compiler Pro Edition: User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

A.2.1.2.2. Reviewing Loops and Blocks in Your Component or Task

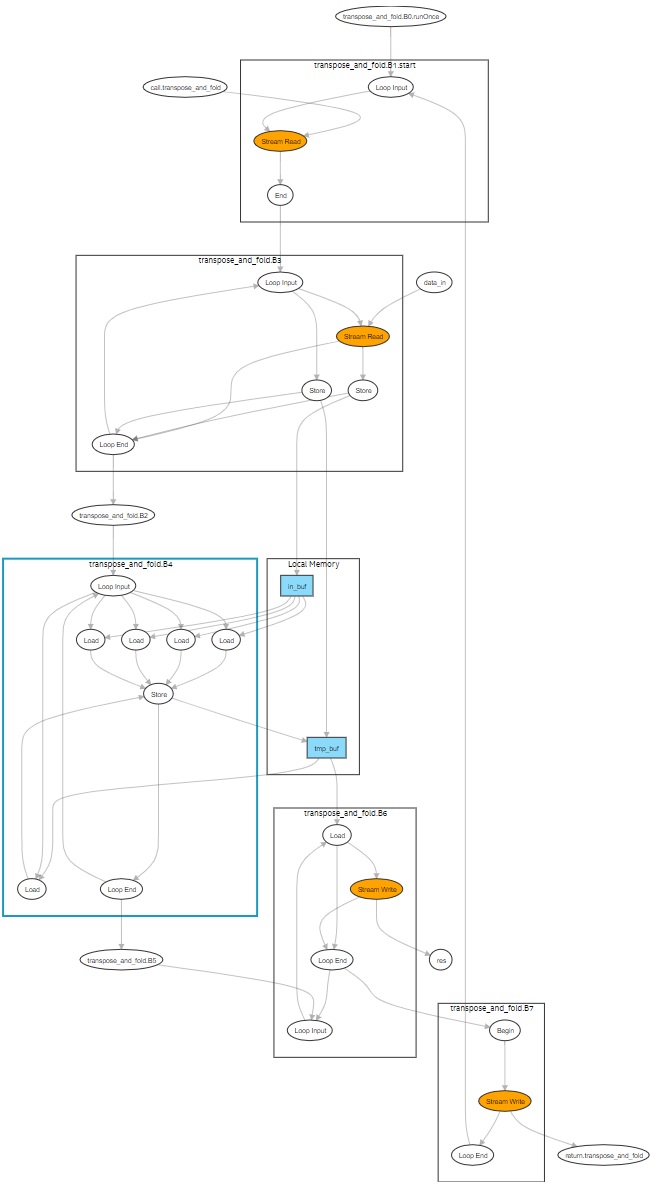

The Function Views of the System Viewer in the High Level Design Report (report.html) shows an abstracted netlist of your component design. In the Function Views, you can visualize loops in your component and your component interactions with its internal RAM block and external interfaces.

#include "HLS/hls.h"

#include <stdio.h>

#include <stdlib.h>

#define SIZE 4

typedef ihc::stream_in<int> my_operand;

typedef ihc::stream_out<int> my_result;

component void transpose_and_fold(my_operand &data_in, my_result &res)

{

int i;

int j;

int in_buf[SIZE][SIZE] hls_memory;

int tmp_buf[SIZE][SIZE] hls_memory;

for (i = 0; i < SIZE * SIZE; i++) {

in_buf[i / SIZE][i % SIZE] = data_in.read();

tmp_buf[i / SIZE][i % SIZE] = 0;

}

#ifdef USE_IVDEP

#pragma ivdep safelen(SIZE)

#endif

for (j = 0; j < SIZE * SIZE * SIZE; j++) {

#pragma unroll

for (i = 0; i < SIZE; i++) {

tmp_buf[j % SIZE][i] += in_buf[i][j % SIZE];

}

}

for (i = 0; i < SIZE * SIZE; i++) {

res.write(tmp_buf[i / SIZE][i % SIZE]);

}

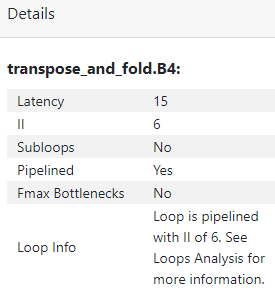

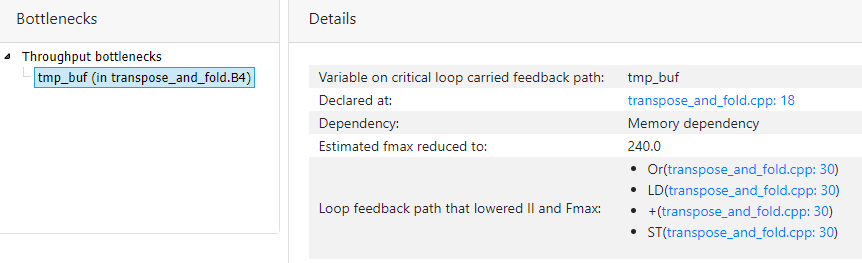

}The Details pain in the report shows that transpose_and_fold.B4 is a pipelined loop with an II value of 6. The loop pipeline with this II value might affect the throughput of your design.

You can investigate further by checking the Loop Analysis report.

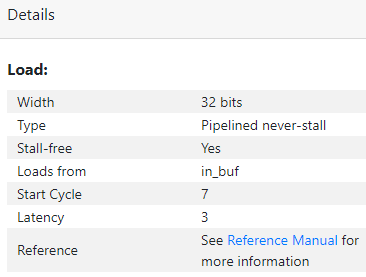

To see more information about the LSU in the System Viewer report, click on a node to display information about the LSU in the Details pane. In the figure below, the Details pane shows information like the latency and that the LSU is stall-free.

For stallable nodes, latency values provided are estimates.

- Control

Control connections are connections between blocks and loops.

- Memory

Memory connections are connections between local memories, agent memories, or Avalon® MM Host interfaces.

- Streams

Stream connections are connections to and from read or write streams