AN 881: PCI Express* Gen3 x16 Avalon® Memory Mapped (Avalon-MM) DMA with DDR4 SDRAM and HBM2 Memories Reference Design

2.3. PCIe Avalon-MM DMA Reference Design with External and HBM2 Memories Platform Designer System

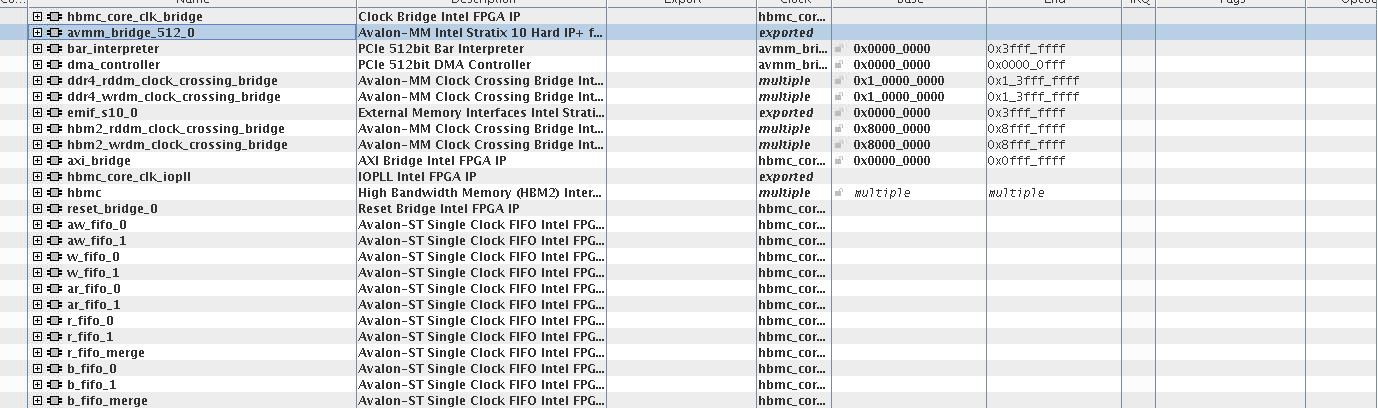

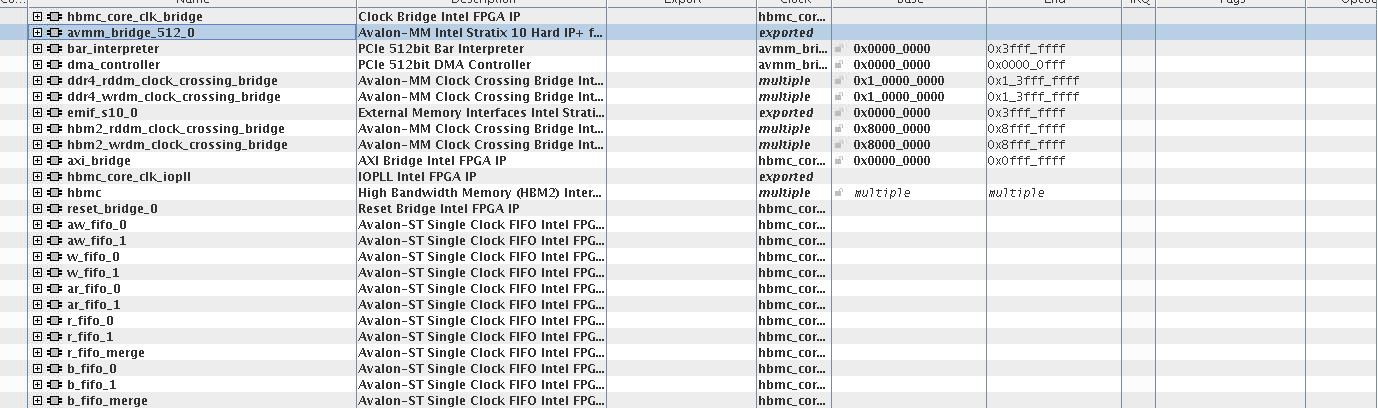

The following image shows the modules in the Platform Designer system for this reference design.

Figure 7. Avalon® -MM Intel® Stratix® 10 Hard IP+ for PCI Express* with External and HBM2 Memories Platform Designer System

| Interface | Base and End Addresses | Bursting Avalon Master (BAM) BAR |

|---|---|---|

| Intel DMA Controller | 0x0000_0000 - 0x0000_0fff | BAR0 |

| HBM2 Memory Controller | 0x8000_0000 - 0x8fff_ffff | BAR2 |

| Intel DDR4 Controller | 0x1_0000_0000 - 0x1_3fff_ffff | BAR4 |

| Port | Function | Description |

|---|---|---|

| RDDM | Read Data Mover | This interface transfers DMA data from the PCIe* system memory to the memory in Avalon® -MM address space. |

| WRDM | Write Data Mover | This interface transfers DMA data from the memory in Avalon® -MM address space to the PCIe* system memory. |

| BAM | Bursting Avalon® -MM Master | This interface provides host access to the registers and memory in Avalon® -MM address space. The Bursting Avalon® -MM Master module converts PCIe* Memory Reads and Writes to Avalon® -MM Reads and Writes. |

| Intel DDR4 Controller | DDR4 Controller | This is a single-port DDR4 controller with 64 DQ width and 8 DQ per DQS group. |

| HBM2 Memory Controller | HBM Controller | This is a single channel with 2 pseudo channel HBM Controllers. The user interface to the HBM2 Controller uses the AXI4 protocol. Each Controller has one AXI4 interface per pseudo channel or 2 AXI4 interfaces per channel. |