F-Tile CPRI PHY Intel® FPGA IP Design Example User Guide

ID

683281

Date

12/13/2021

Public

A newer version of this document is available. Customers should click here to go to the newest version.

1.1. Hardware and Software Requirements

1.2. Generating the Design

1.3. Directory Structure

1.4. Simulating the Design Example Testbench

1.5. Compiling the Compilation-Only Project

1.6. Compiling and Configuring the Design Example in Hardware

1.7. Testing the Hardware Design Example

1.8. Transceiver Toolkit

1.2. Generating the Design

Procedure

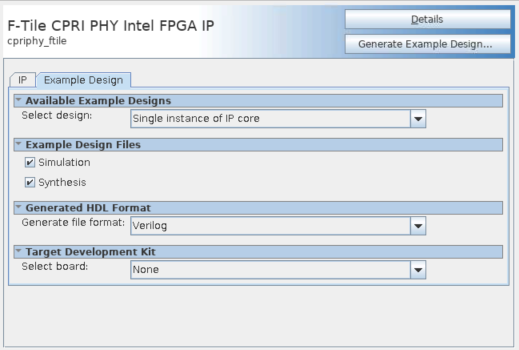

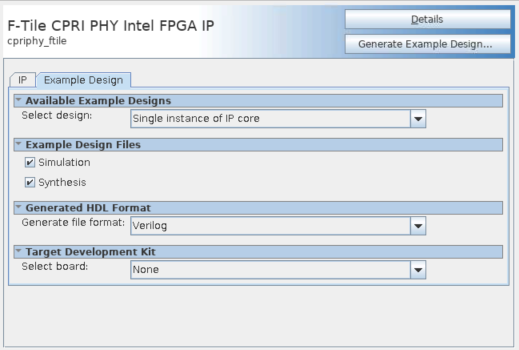

Example Design Tab in IP Parameter Editor

To create an Intel® Quartus® Prime Pro Edition project:

- In the Intel® Quartus® Prime Pro Edition software, click File > New Project Wizard to create a new project, or File > Open Project to open an existing project. The wizard prompts you to specify a device.

- Specify the device family Agilex (I-series) and select a device that meets all of these requirements:

- Transceiver tile: F-tile

- Transceiver speed grade: -1 or -2

- Core speed grade: -1 or -2 or -3

- Click Finish.

Follow these steps to generate the F-Tile CPRI PHY Intel® FPGA IP hardware design example and testbench:

- In the IP Catalog, locate and select F-Tile CPRI PHY Intel® FPGA IP. The New IP Variation dialog box appears.

- Specify a top-level name for your custom IP variation. The parameter editor saves the IP variation settings in a file named <your_ip> .ip.

- Click OK. The parameter editor appears.

- On the IP tab, specify the parameters for your IP core variation.

- On the Example Design tab, under Example Design Files, select the Simulation option to generate the testbench and the compilation-only project. Select the Synthesis option to generate the hardware design example. You must select at least one of the Simulation and Synthesis options to generate the design example.

- On the Example Design tab, under Generated HDL Format, select Verilog HDL or VHDL. If you select VHDL, you must simulate the testbench with a mixed-language simulator. The device under test in the ex_<datarate> directory is a VHDL model, but the main testbench file is a SystemVerilog file.

- Click the Generate Example Design button. The Select Example Design Directory dialog box appears.

- If you want to modify the design example directory path or name from the defaults (cpriphy_ftile_0_example_design), browse to the new path and type the new design example directory name (<design_example_dir>).