ModelSim* - Intel® FPGA Edition Simulation Quick-Start: Intel® Quartus® Prime Standard Edition

ID

683248

Date

12/30/2019

Public

1.2. Specify EDA Tool Settings

Specify EDA tool settings to generate simulation files for supported simulators.

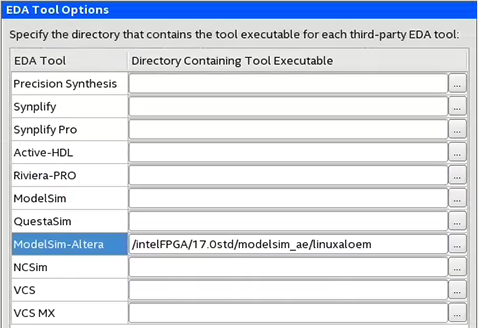

- In the Intel® Quartus® Prime software, click Tools > Options > EDA Tool Options.

- To specify the location of your simulator for integration with the Intel® Quartus® Prime software, click Tools > Options > EDA Tool Options.

Figure 1. EDA Tool Options

- In ModelSim-Altera, enter the ModelSim* - Intel® FPGA Edition executable path. Select the appropriate ModelSim* - Intel® FPGA Edition executable, rather than any other supported ModelSim* software.

- /intelFPGA_lite/<version>/modelsim_ase/win32aloem (Lite)

- /intelFPGA/<version>/modelsim_ase/win32aloem (Standard)

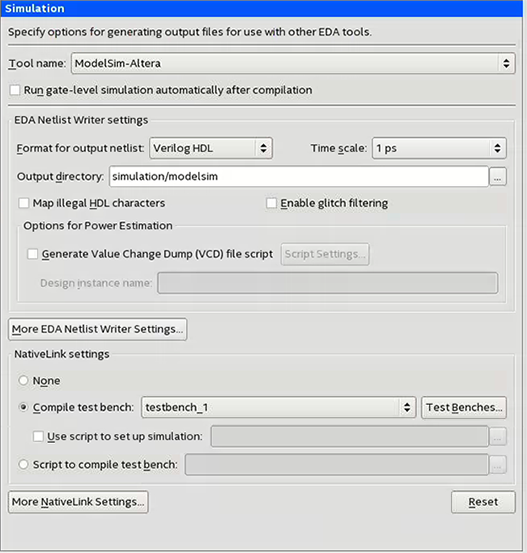

- Click Assignments > Settings > EDA Tool Settings > Simulation.

- On the Simulation page, specify the following values for the options:

Option Value Tool name ModelSim-Altera Run gate-level simulation automatically after compilation Disable checkbox Format for output netlist Verilog HDL Map illegal VHDL characters Disable checkbox Enable glitch filtering Disable checkbox Generate Value Change Dump (VCD) file script Disable checkbox Figure 2. Simulation Options

- Under NativeLink settings, select the Compile test bench option, and then click the Test Benches button.

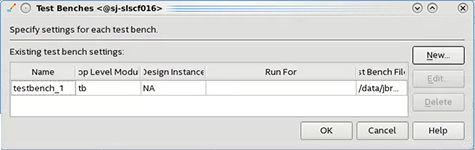

- Click New. Specify testbench_1 as the Test bench name, and tb as the Top level module in test bench.

- Under Test bench and simulation files, enter or select the testbench_1.v file, click Add, and then click OK. The Test Benches dialog box displays the properties of the testbenches in your project.

Figure 3. Test Benches Dialog Box

- In the Test Benches dialog box, click OK. In the Settings dialog box, click OK.