Quartus® Prime Pro Edition User Guide: Design Compilation

ID

683236

Date

9/30/2024

Public

A newer version of this document is available. Customers should click here to go to the newest version.

1.1. Compilation Overview

1.2. Design Analysis & Elaboration

1.3. Design Synthesis

1.4. Design Place and Route

1.5. Incremental Optimization Flow

1.6. Fast Forward Compilation Flow

1.7. Full Compilation Flow

1.8. HSSI Dual Simplex IP Generation Flow

1.9. Exporting Compilation Results

1.10. Clearing Compilation Results

1.11. Integrating Other EDA Tools

1.12. Compiler Optimization Techniques

1.13. Compilation Monitoring Mode

1.14. Viewing Quartus Database File Information

1.15. Understanding the Design Netlist Infrastructure

1.16. Using Synopsys* Design Constraint (SDC) on RTL Files

1.17. Using the Node Finder

1.18. Synthesis Language Support

1.19. Synthesis Settings Reference

1.20. Fitter Settings Reference

1.21. Design Compilation Revision History

2.1. Factors Affecting Compilation Results

2.2. Strategies to Reduce the Overall Compilation Time

2.3. Reducing Synthesis Time

2.4. Reducing Placement Time

2.5. Reducing Routing Time

2.6. Reducing Static Timing Analysis Time

2.7. Setting Process Priority

2.8. Reducing Compilation Time Revision History

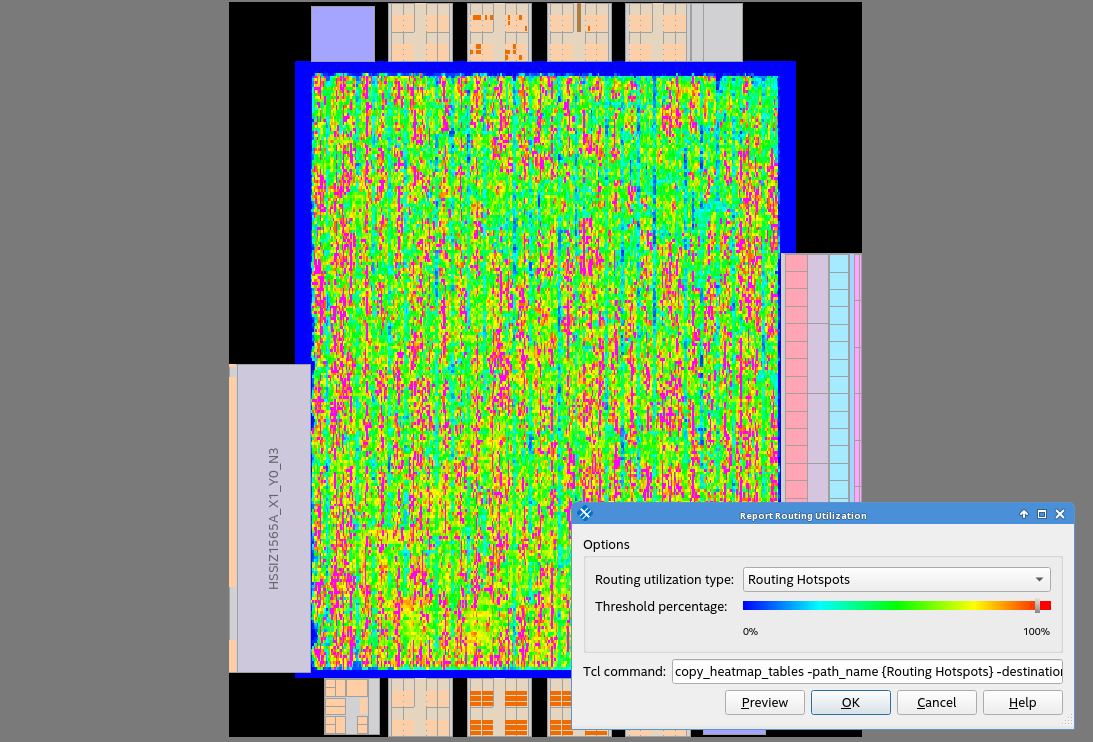

2.5.1.2. Identifying Routing Congestion with the Chip Planner

The Chip Planner provides a comprehensive visual overview of device resources, including detailed congestion visualization. This is facilitated by the Report Routing Utilization Task, which presents precise percentages of routing utilization across different utilization types in the current compilation. Utilizing a configurable color scale, it offers a clear representation of congestion levels.

For guidance on configuring the Report Routing Utilization Task, refer to " Viewing Routing Congestion in Chip Planner " in the Intel Quartus Prime Pro Edition User Guide: Design Optimization .