External Memory Interfaces Intel® Agilex™ FPGA IP User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

3.3.4.1.2. DDR4 Write Calibration

Write Leveling

Write leveling calibration aligns the write DQS to the memory clock, to compensate for skews. In general, leveling calibration tries a variety of delay values to determine the edges of the write window, and then selects an appropriate value to center the window.

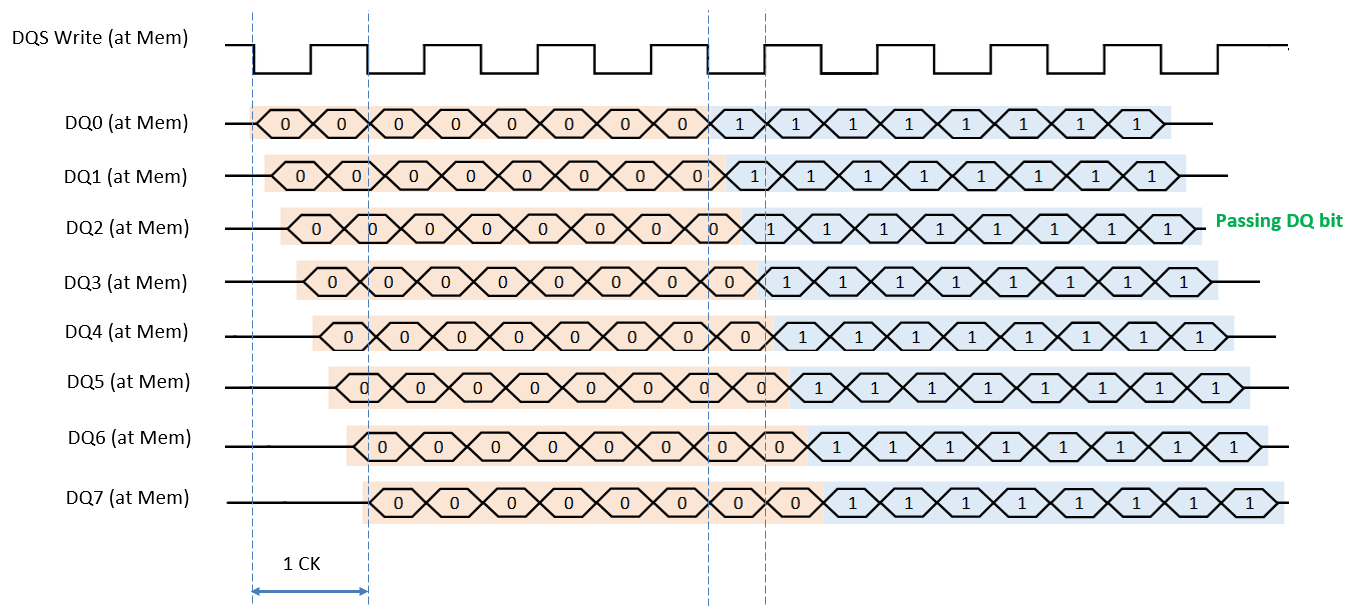

Write leveling occurs before write deskew, therefore only one successful DQ bit is required to register a pass. Write leveling staggers the write DQ bus to ensure that at least one DQ bit falls within the valid write window.

Write Deskew

Write Deskew performs per-bit deskew of write data relative to the write strobe and clock. Write deskew calibration does not change dqs_out delays; the write DQS is aligned to the CK clock during write leveling.

VREF-OUT Calibration

VREF-OUT calibration tunes the VREF setting at DDR4 memory device by using mode register set (MRS) commands. The VREF-OUT calibration algorithm is similar to the VREF-IN calibration algorithm. The algorithm picks the VREF-OUT setting that gives the best write window.