External Memory Interfaces Intel® Agilex™ FPGA IP User Guide

A newer version of this document is available. Customers should click here to go to the newest version.

3.3.4.1. Calibration Algorithms for DDR4

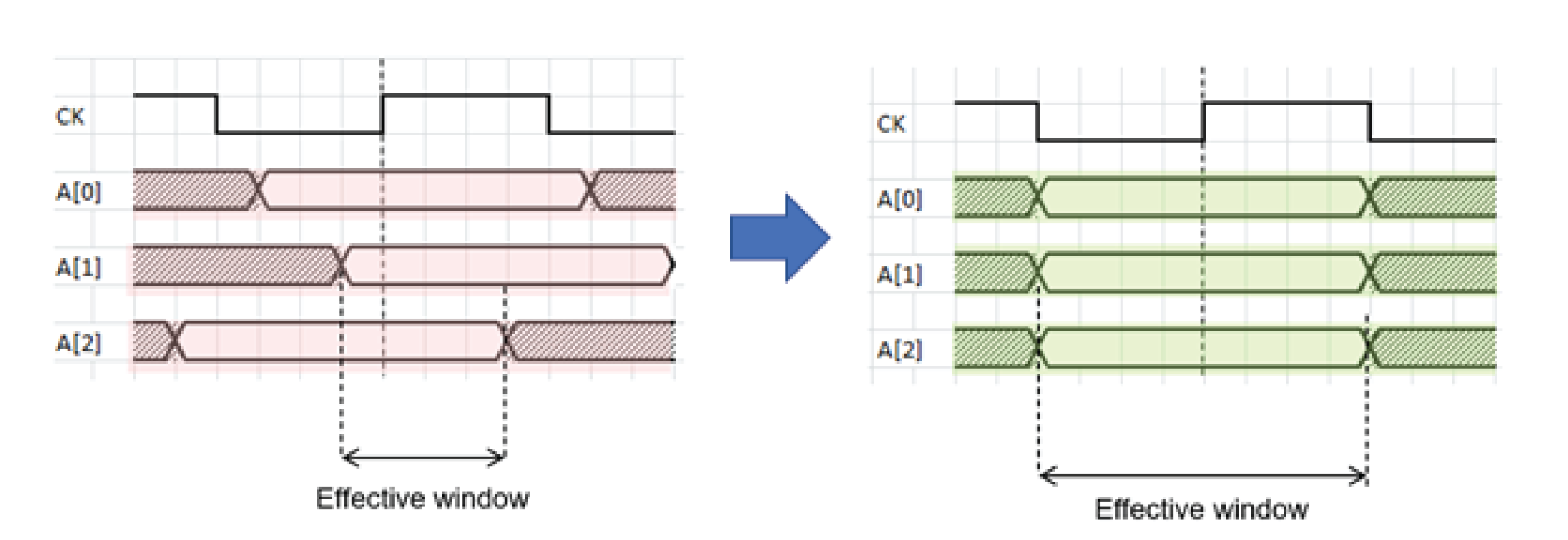

Leveling Calibration

The FPGA toggles the CS# and CAS#/A15 signals while keeping other address and command signals constant, to send READ commands to memory, and monitors whether the DQS signal toggles. If the DQS signal toggles, it indicates that the READ commands have been accepted. The algorithm then repeats using different delay values, to find the optimal window. This stage moves the entire address and command bus with CS#.

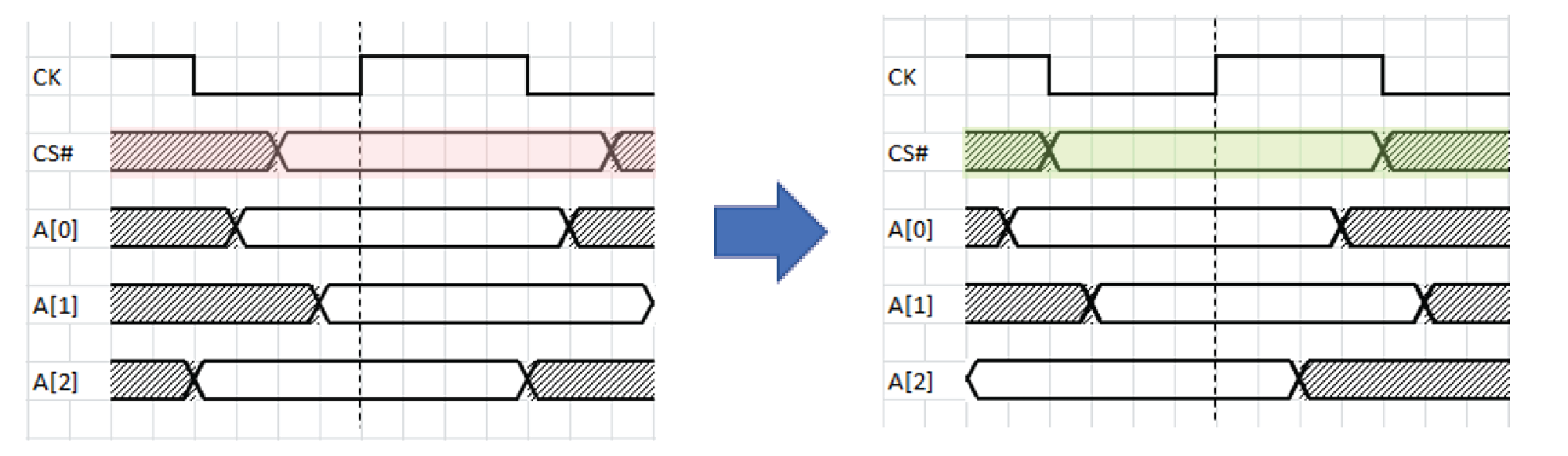

Deskew Calibration

Deskew calibration uses the DDR4 address and command parity feature; you should not omit these pins from your design. The deskew calibration cannot deskew ODT and CKE pins because these signals are not in included in the address and command parity calculation.

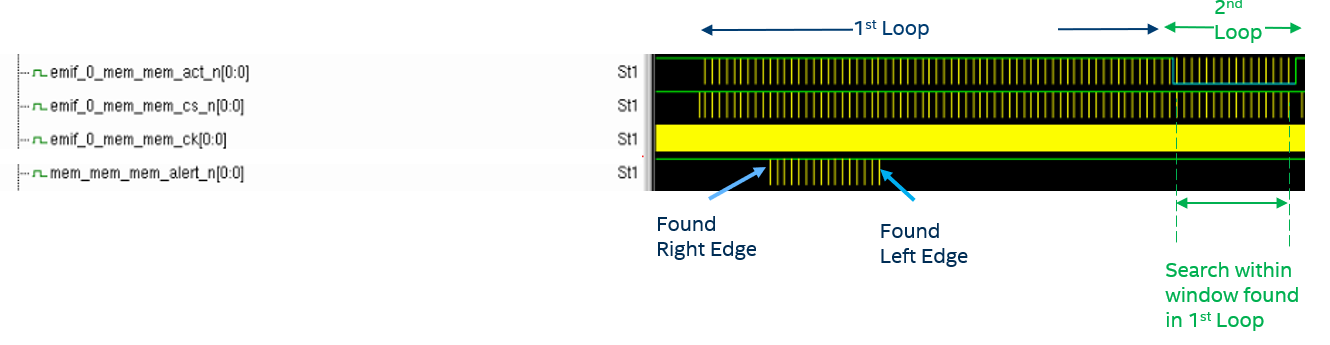

The deskew calibration test consists of two loops. In the first loop, the FPGA adjusts the delays on an address and command pin to send the address parity bit; the DDR4 memory device responds with an alert signal if it detects the parity bit. The test repeats this process for all other address and command signals, except for the ODT and CKE signals. The first loop detects the union of windows if there are multiple components within the same rank. For a sub-optimal board layout, the window detected in the first loop may be greater than 1 memory clock cycle.

In the second loop, the algorithm inverts the parity injection pattern and sweeps the delay within the window found in the first loop. The alert signal does not toggle in the second loop when all memory components in the same rank receive the command correctly. This check detects the intersection of the windows and improves the accuracy of the address and command deskew