AN 780: Compiling and Customizing an Intel® Arria® 10 Custom Platform for OpenCL*

ID

683045

Date

10/30/2018

Public

1.1. Introduction to Custom Platforms

1.2. OpenCL System Architecture

1.3. Hierarchical Structure of the Intel® Arria® 10 GX FPGA Development Kit Reference Platform's Hardware

1.4. Intel® Quartus® Prime Software Revisions Describing the Custom Platform

1.5. Intel® FPGA SDK for OpenCL™ and User Environment Setup

1.6. Intel® Arria® 10 Custom Platform Project Setup and Customization Procedure

1.7. Intel® Arria® 10 Custom Platform Customization Example

1.8. Updating Your Custom Platform to Target a Different Device

1.9. Migrating the Custom Platform between Different Intel® Quartus® Prime Software Versions

1.10. Document Revision History for Compiling and Customizing an Intel® Arria® 10 Custom Platform for OpenCL*

1.7.1. Modifying the board.qsys File in the Custom Platform

1.7.2. Modifying the Kernel (freeze_wrapper.v and board_spec.xml)

1.7.3. Updating the Top-Level I/O Ring with the Modified board.qsys and freeze_wrapper.v Files

1.7.4. Updating the Original Custom Platform Directory with the New Custom Platform Modifications

1.7.5. Compilation Log Files

1.7.6. Analyzing the Results from Compilation

1.7.1.1. Opening an Existing Intel® Quartus® Prime Project and the board.qsys Platform Designer System Design

1.7.1.2. Adding the Avalon® -ST Single Clock FIFO Component into the Platform Designer System

1.7.1.3. Connecting the Avalon® -ST Single Clock FIFO Component's Exported Signals in the Top-Level Platform Designer System

1.7.2.1. Opening an Existing Intel® Quartus® Prime Project and the kernel_system.qsys Platform Designer System Design

1.7.2.2. Adding an Avalon® -ST Adapter Component into the Platform Designer System

1.7.2.3. Connecting the Avalon® -ST Adapter Component's Exported Signals in the Top-Level Platform Designer System

1.7.2.4. Modifying the board_spec.xml File

1.7.2.5. Modifying the freeze_wrapper.v File

1.7.1.2. Adding the Avalon® -ST Single Clock FIFO Component into the Platform Designer System

Add an Avalon® -ST Single Clock FIFO component to the board.qsys Platform Designer system.

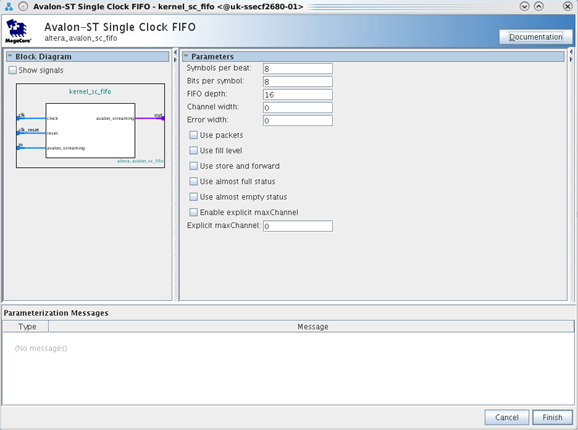

- With board.qsys opened in Platform Designer, add an Avalon® -ST Single Clock FIFO component from the IP catalog. Open the parameter editor and specify the following configuration settings:

Figure 6. Configuration Settings of the Avalon® -ST Single Clock FIFO Component

- Click Finish.

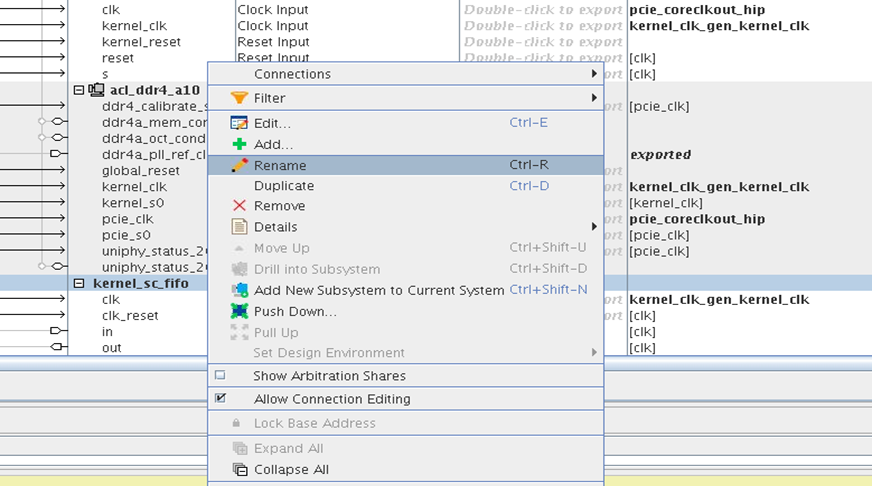

- Right-click the board_sc_fifo component at the bottom of the System Contents tab and select Rename.

Figure 7. Renaming the board_sc_fifo component to kernel_sc_fifo

- Change the component’s name to kernel_sc_fifo.

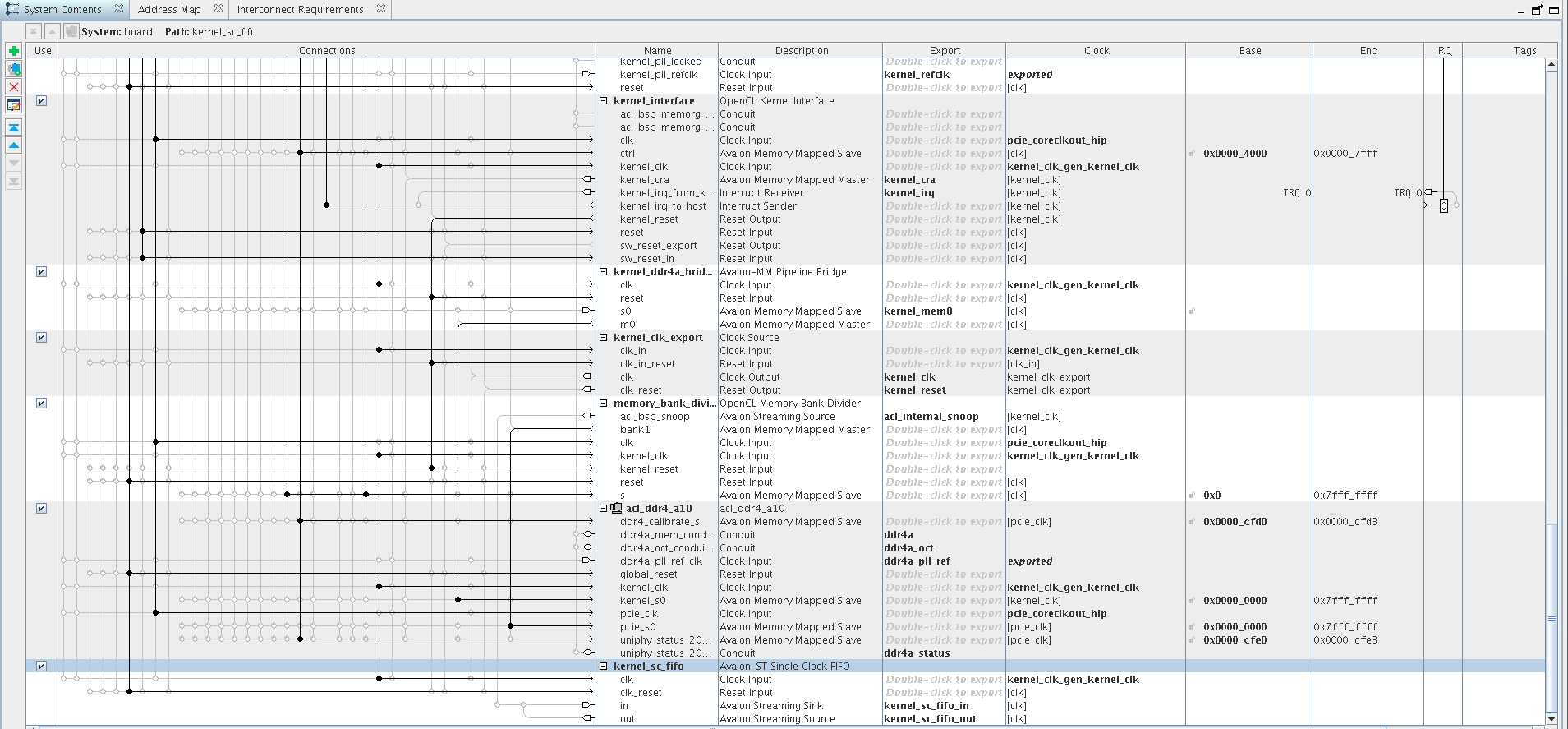

- Connect the kernel_sc_fifo component’s clock input interface to the kernel clock by performing the following tasks:

- Right-click the clock interface of the kernel_sc_fifo component.

- Click Connections > kernel_sc_fifo.clock and then select kernel_clk_gen.kernel_clk.

- Connect the reset interface of the kernel_sc_fifo component to the PCIe reset.

- Right-click the reset interface of the kernel_sc_fifo component.

- Click Connections > kernel_sc_fifo.reset and then select kernel_interface.kernel_reset.

- Export the in and out interfaces of the Avalon® -ST Single Clock FIFO component by double-clicking the Export column in the System Contents tab.

The in and out ports are named kernel_sc_fifo_in and kernel_sc_fifo_out, respectively.Figure 8. In and Out Ports of the Avalon® -ST Single Clock FIFO Component

- Verify that there are no errors in the message window.