A newer version of this document is available. Customers should click here to go to the newest version.

Intel® oneAPI FPGA Handbook

Introduction To FPGA Design Concepts

Intel oneAPI FPGA Development

Defining a Kernel for FPGAs

Debugging and Verifying Your Design

Analyzing Your Design

Optimizing Your Kernel

Optimizing Your Host Application

Integrating Your RTL IP Core Into a System

RTL IP Core Kernel Interfaces

Loops

Pipes

Data Types and Arithmetic Operations

Parallelism

Memories and Memory Operations

Libraries

Additional FPGA Acceleration Flow Considerations

Additional SYCL* HLS Flow Considerations

FPGA Optimization Flags, Attributes, Pragmas, and Extensions

Quick Reference

Additional Information

Document Revision History for the Intel oneAPI FPGA Handbook

Notices and Disclaimers

Refactor the Loop-Carried Data Dependency

Relax Loop-Carried Dependency

Transfer Loop-Carried Dependency to Local Memory

Minimize the Memory Dependencies for Loop Pipelining

Unroll Loops

Fuse Loops to Reduce Overhead and Improve Performance

Optimize Loops With Loop Speculation

Remove Loop Bottlenecks

Improve fMAX/II with Shannonization

Optimize Inner Loop Throughput

Improve Loop Performance by Caching Data in On-Chip Memory

Global Memory Bandwidth Use Calculation

Manual Partition of Global Memory

Partitioning Buffers Across Different Memory Types (Heterogeneous Memory)

Partitioning Buffers Across Memory Channels of the Same Memory Type

Ignoring Dependencies Between Accessor Arguments

Contiguous Memory Accesses

Static Memory Coalescing

Use SYCL Shared Library With Third-Party Applications

Use of RTL Libraries for FPGA

Object Manifest File Syntax of an RTL Library

Restrictions and Limitations in RTL Support

Intel® Stratix® 10 and Intel Agilex® 7 Design-Specific Reset Requirements for Stall-Free and Stallable RTL Libraries

Stall-Free RTL

Specify Schedule FMAX Target for Kernels (-Xsclock=<clock target>)

Create a 2xclock Interface (-Xsuse-2xclock)

Disable Burst-Interleaving of Global Memory (-Xsno-interleaving=<global_memory_name>)

Force Ring Interconnect for Global Memory (-Xsglobal-ring)

Force a Single Store Ring to Reduce Area (-Xsforce-single-store-ring)

Force Fewer Read Data Reorder Units to Reduce Area (-Xsnum-reorder)

Disable Hardware Kernel Invocation Queue (-Xsno-hardware-kernel-invocation-queue)

Modify the Handshaking Protocol Between Clusters (-Xshyper-optimized-handshaking)

Disable Automatic Fusion of Loops (-Xsdisable-auto-loop-fusion)

Fuse Adjacent Loops With Unequal Trip Counts (-Xsenable-unequal-tc-fusion)

Pipeline Loops in Non-task Kernels (-Xsauto-pipeline)

Control Semantics of Floating-Point Operations (-fp-model=<value>)

Modify the Rounding Mode of Floating-point Operations (-Xsrounding=<rounding_type>)

Global Control of Exit FIFO Latency of Stall-free Clusters (-Xssfc-exit-fifo-type=<value>)

Enable the Read-Only Cache for Read-Only Accessors (-Xsread-only-cache-size=<N>)

Control Hardware Implementation of the Supported Data Types and Math Operations (-Xsdsp-mode=<option>)

Generate Register Map Wrapper (-Xsregister-map-wrapper-type)

Pipes Extension

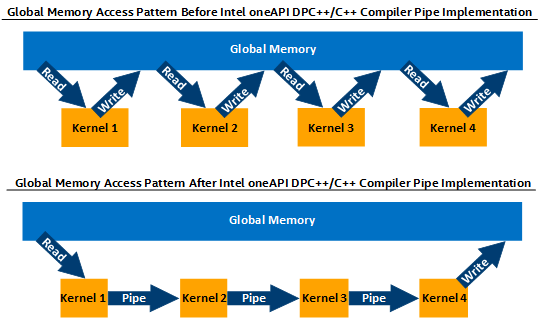

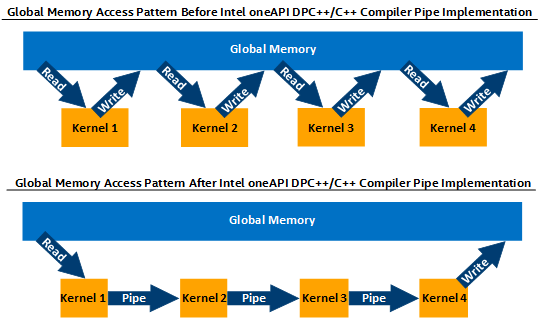

Using global memory to communicate data between your kernels can constrain the performance of your design. DPC++ pipes provide a mechanism for passing data between kernels and synchronizing kernels with high efficiency and low latency. DPC++ pipes allow kernels to use on-device FIFO buffers to communicate directly with each other. The memory model of pipes allows them to be used for inter-kernel communication without waiting for kernel completion or involvement of the host processor, as shown in the following figure:

Using SYCL* Pipes to Decouple Data Movement between Concurrently Executing Kernels

Parent topic: Pipes