A newer version of this document is available. Customers should click here to go to the newest version.

3.1.1. HDMI RX-TX Retransmit With Integrated Transceiver Design Parameters

3.1.2. Integrated Transceiver With Dual Simplex Block Diagram

3.1.3. Integrated Transceiver Without Dual Simplex Block Diagram

3.1.4. Agilex™ 5 HDMI RX-TX Retransmit With Integrated Transceiver Design Example Top Level Common Blocks

3.1.5. Agilex™ 5 HDMI RX-TX Retransmit With Integrated Transceiver Design Example Interface Signals

3.2.1. HDMI RX-TX Retransmit Without Integrated Transceiver Design Parameters

3.2.2. Non-Integrated Transceiver With Dual Simplex Block Diagram

3.2.3. Non-Integrated Transceiver Without Dual Simplex block diagram

3.2.4. Agilex™ 5 HDMI RX-TX Retransmit Without Integrated Transceiver Design Example Top Level Common Blocks

3.2.5. Agilex™ 5 HDMI RX-TX Retransmit Without Integrated Transceiver Design Example Interface Signals

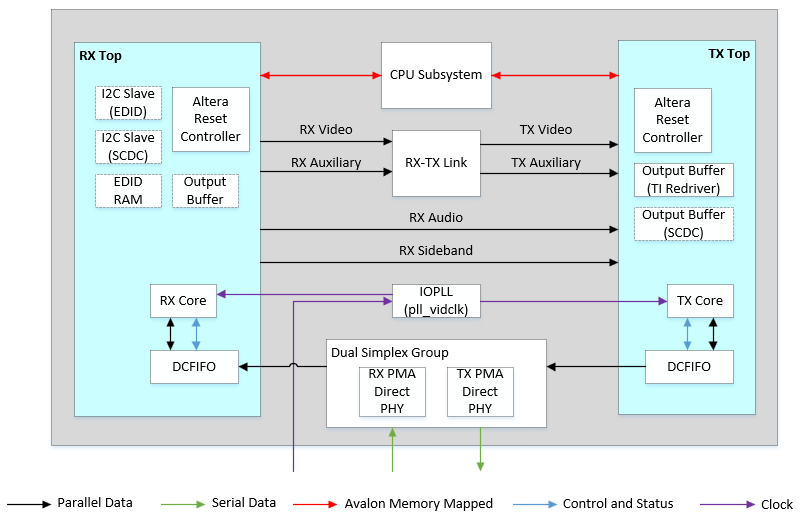

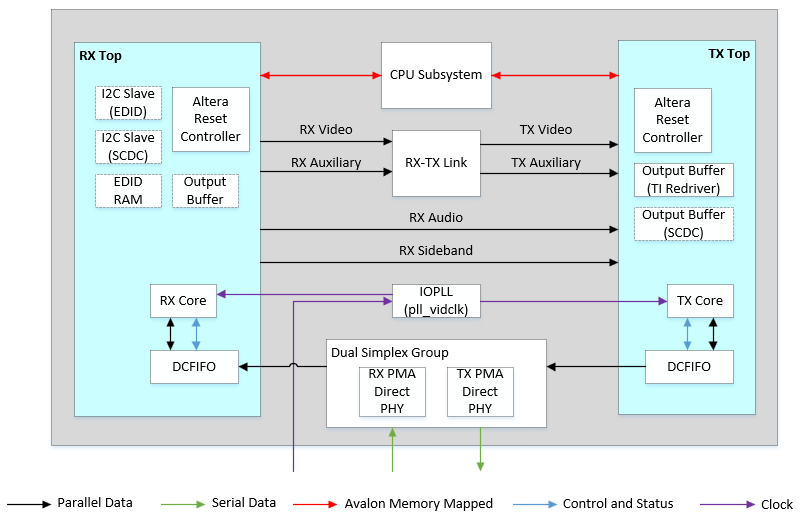

3.2.2. Non-Integrated Transceiver With Dual Simplex Block Diagram

For designs without Integrated Transceiver, the Transceiver IP is located outside of HDMI IP. The Transceiver IP is instantiated at the top level module. For this mode, you can change the transceiver setting based on your need. PMA Direct PHY RX and TX are wrapped into a dual simplex (DS) group. Both RX and TX transceiver are placed at the same channel.

The RX and TX simplex IPs are merged into a dual simplex group with the Assignment Editor. For more information about implementing dual simplex interfaces, refer to "Implementing Dual Simplex Interfaces" in the GTS Transceiver Dual Simplex Interfaces User Guide .

Figure 11. Dual Simplex Assignment Editor

Figure 12. HDMI RX-TX Retransmit Block Diagram (with Dual Simplex)