External Memory Interfaces Agilex™ 7 M-Series FPGA IP Design Example User Guide

ID

772632

Date

4/01/2024

Public

A newer version of this document is available. Customers should click here to go to the newest version.

1. About the External Memory Interfaces Agilex™ 7 M-Series FPGA IP

2. Design Example Quick Start Guide for External Memory Interfaces Agilex™ 7 M-Series FPGA IP

3. Design Example Description for External Memory Interfaces Agilex™ 7 M-Series FPGA IP

4. Document Revision History for External Memory Interfaces Agilex™ 7 M-Series FPGA IP Design Example User Guide

2.1. Creating an EMIF Project

2.2. Generating and Configuring the EMIF IP

2.3. Configuring DQ Pin Swizzling

2.4. Generating the Synthesizable EMIF Design Example

2.5. Generating the EMIF Design Example for Simulation

2.6. Pin Placement for Agilex™ 7 M-Series EMIF IP

2.7. Compiling the Agilex™ 7 M-Series EMIF Design Example

2.8. Using the EMIF Design Example with the Test Engine IP

2.9. Generating the EMIF Design Example with the Performance Monitor

2.1.1.3.1. Generating a Custom Memory Preset File for DDR4

2.1.1.3.2. Guidelines for Selecting the DDR4 DRAM Component Package Type

2.1.1.3.3. Generating a Custom Memory Preset File for DDR5

2.1.1.3.4. Guidelines for Selecting the DDR5 DRAM Component Package Type

2.1.1.3.5. Generating a Custom Memory Preset File for LPDDR5

2.3.1. Example: DQ Pin Swizzling Within DQS group for x32 DDR4 interface

2.3.2. Example: Byte Swizzling for a x32 DDR4 interface, using a memory device of x8 width

2.3.3. Combining Pin and Byte Swizzling

2.3.4. Example: Swizzling for a x32 + ECC interface

2.3.5. Example: Byte Swizzling for Lockstep Configuration

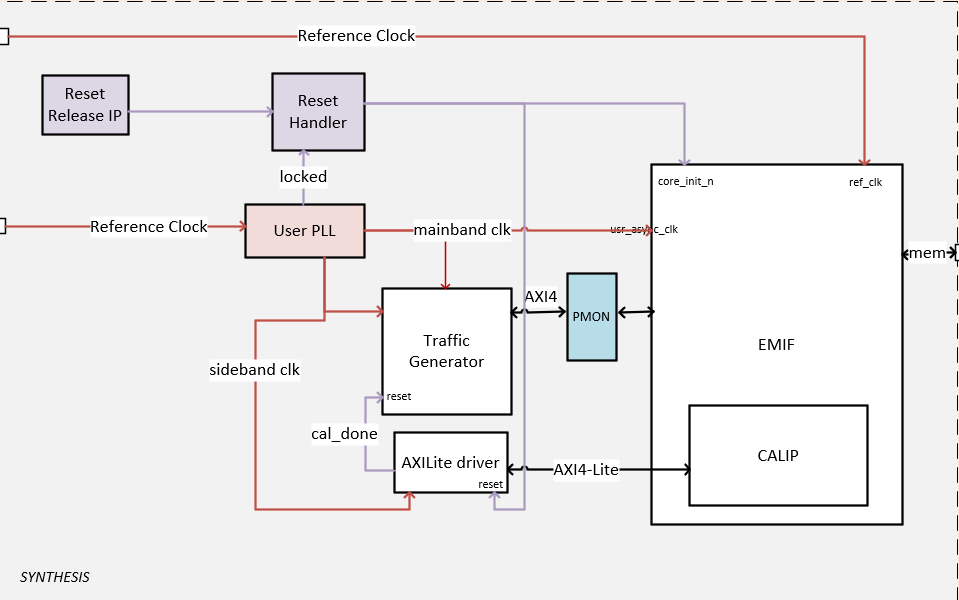

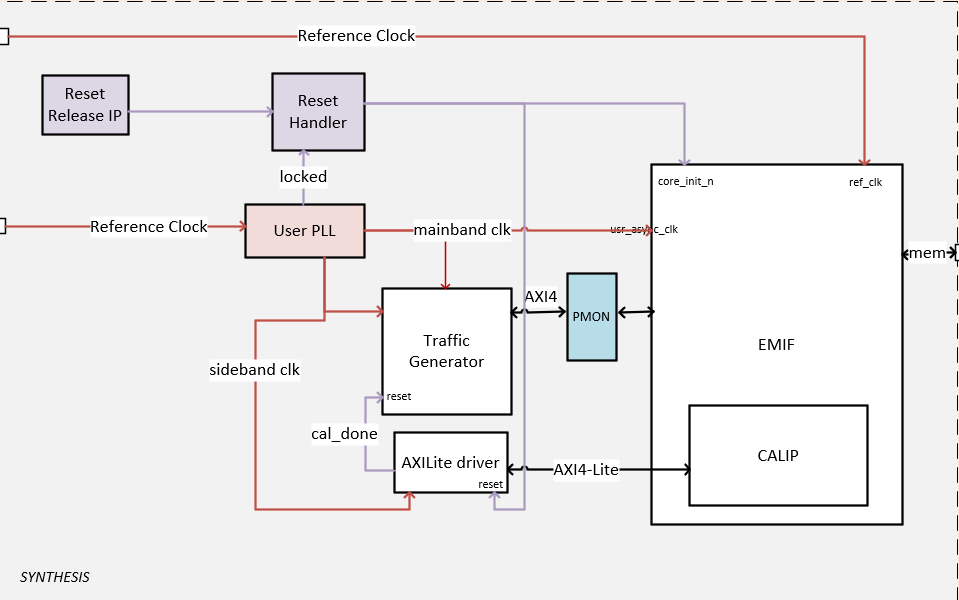

3.1. Synthesis Design Example

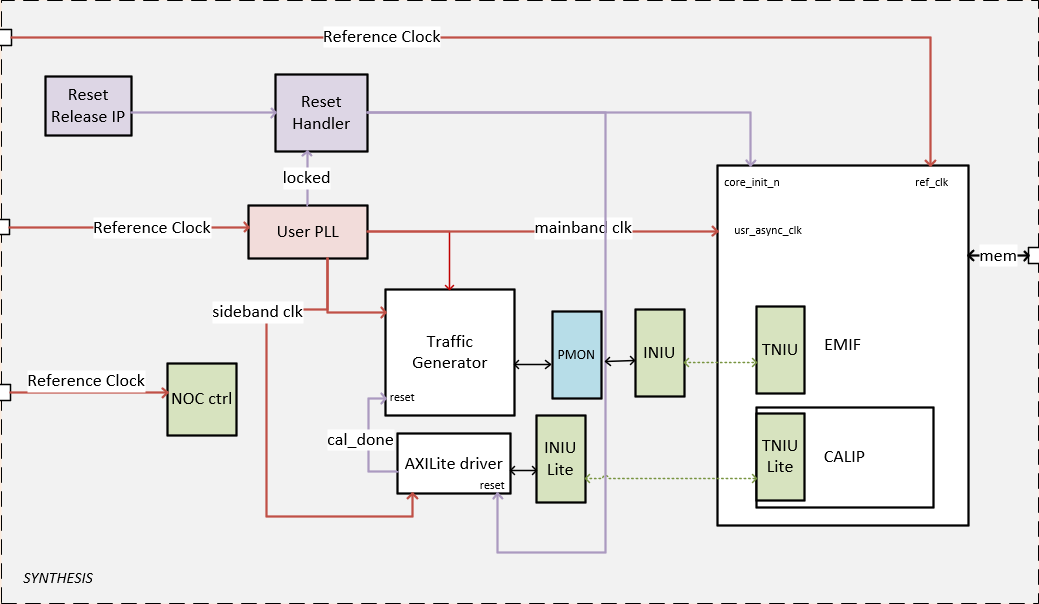

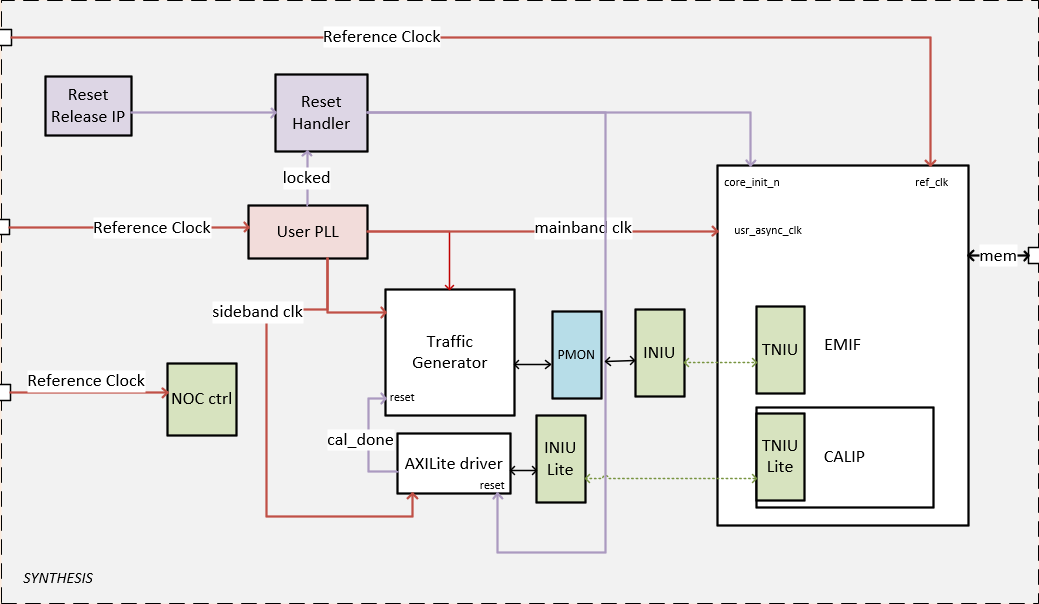

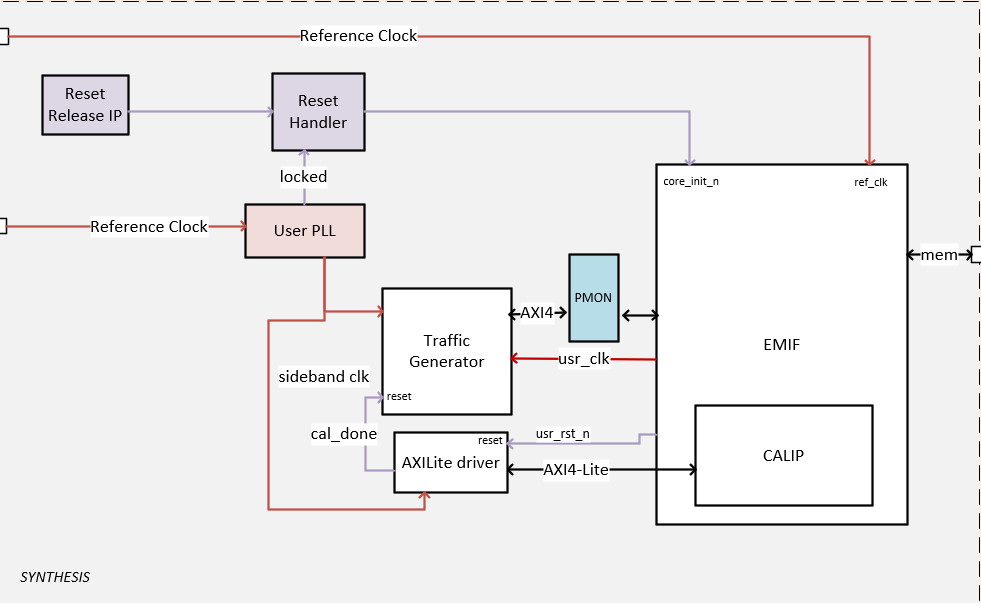

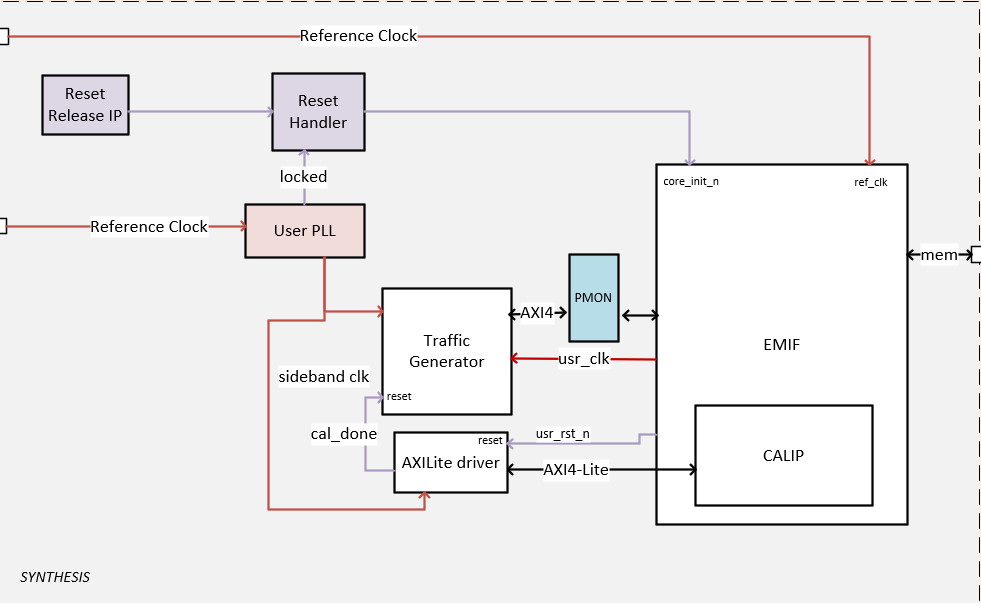

The synthesis design example contains the major blocks shown in the figure below.

- A traffic generator is a synthesizable AXI4 driver that implements a hard-coded pattern and monitors the data read from the memory to ensure that it matches the written data, and asserts a failure otherwise. You can select different traffic generator programs when generating the example design. Each program performs the following transactions:

- Single write and read (with AxLEN=axlen_a 1 ) 2

- Single write and read (with AxLEN=axlen_b 1 ) 2

- Sequential address 3 block of m 4 writes and m 4 reads (with AxLEN=axlen_a 1 )

- Sequential address 3 block of m 4 writes and m 4 reads (with AxLEN=axlen_b 1 )

- Random address 5 block of m 4 writes and m 4 reads (with AxLEN=axlen_a 1 )

1 The axlen_a and axlen_b values depend on the memory technology. 2 Repeated for 3 loops in the traffic generator program = Short. 3 Sequential Address pattern starts at address=0, and increments by (AXI_DATA_WIDTH/8)*(AxLEN+1) on each transaction. 4 The m value depends on the traffic generator program. 5 Random address pattern starts at address=0, and uses pseudo-random addresses. Table 19. axlen_a and axlen_b for Different memory Technologies Technology axlen_a axlen_b Notes DDR4 0 0 DDR5 1 0 axlen_b=0 results in Read-Modify-Write or data-masking on the memory side. LPDDR4 3 3 LPDDR5 1 1 Table 20. m value in Different Traffic Generator programs Traffic Generator Program m Short 128 Medium 512 Long 4096 - An instance of the memory interface, which includes:

- A memory controller which implements all the memory commands and protocol-level requirements.

- The PHY, which serves as an interface between the memory controller and external memory devices to perform read and write operations.

Figure 37. Synthesis Design Example Sync Fabric Mode

Figure 38. Synthesis Design Example Async Fabric Mode

Figure 39. Synthesis Design Example NoC Fabric Mode