A newer version of this document is available. Customers should click here to go to the newest version.

4.3.2. Multi-Segment Mode

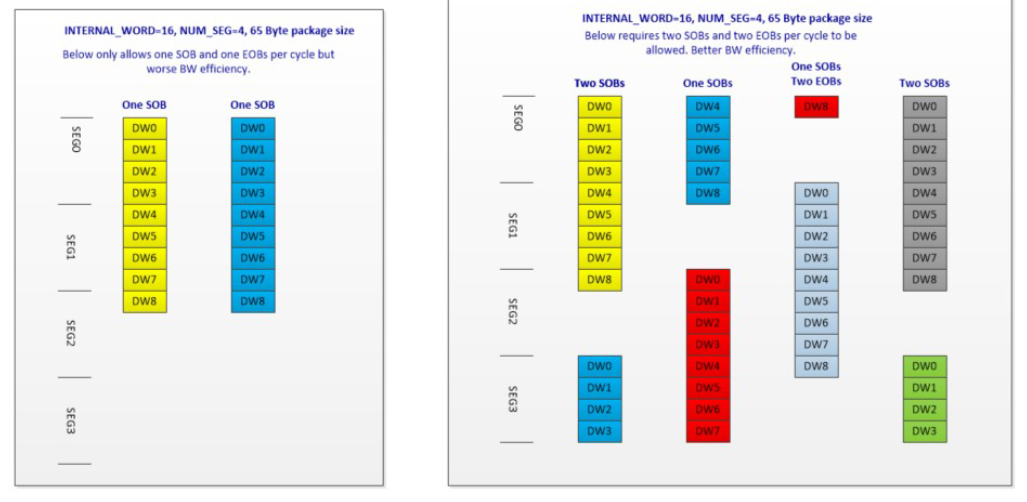

This section describes the functionality of the multi-segment feature of the F-Tile Interlaken Intel® FPGA IP core. This feature enables you to make better use of the transmit and receive bandwidth. For package sizes smaller than the user data width, this feature becomes important to provide better bandwidth efficiency.

The user data interface block contains the multi-segment blocks, TX and RX regroup. In the TX direction, the TX regroup inserts necessary control words based on the user interface control information before sending downstream for further processing. In the RX direction, the control words of the data received from the striper is stripped off to generate the user data and the extracted control word generates the user interface information.

As shown in the figure below, the bandwidth efficiency of the four-segment case is significantly better than the single-segment case. Each segment supports both Interleaved and Packet transfer modes when you operate the IP in multi-segment mode.