Multi Channel DMA Intel® FPGA IP for PCI Express* Design Example User Guide

ID

683517

Date

7/07/2023

Public

A newer version of this document is available. Customers should click here to go to the newest version.

3.5.2.5.1. Build and Install Netdev Driver

3.5.2.5.2. Enable VFs if SRIOV is Supported

3.5.2.5.3. Configure the Number of Channels Supported on the Device

3.5.2.5.4. Configure the MTU Value

3.5.2.5.5. Configure the Device Communication

3.5.2.5.6. Configure Transmit Queue Selection Mechanism

3.5.2.5.7. Test Procedure by Using Name Space Environment

3.5.2.5.8. PIO Test

2.5.2. Hardware Test Results

The Custom Driver was used to generate the following output.

Note: The same test options can be used with DPDK driver and Kernel Mode driver to generate comparable results.

PIO Test

[root@bapvemb005t perfq_app]# ./perfq_app -b 0000:01:00.0 -o -v PIO Write and Read Test ... Pass

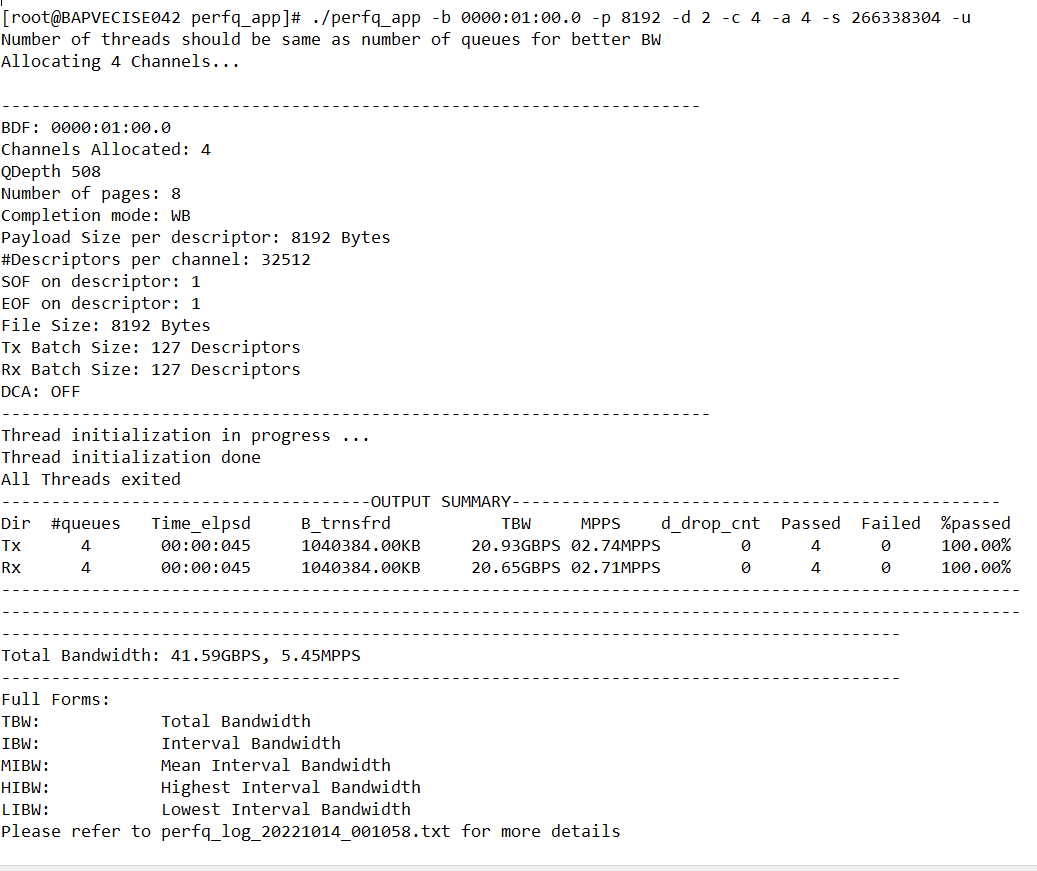

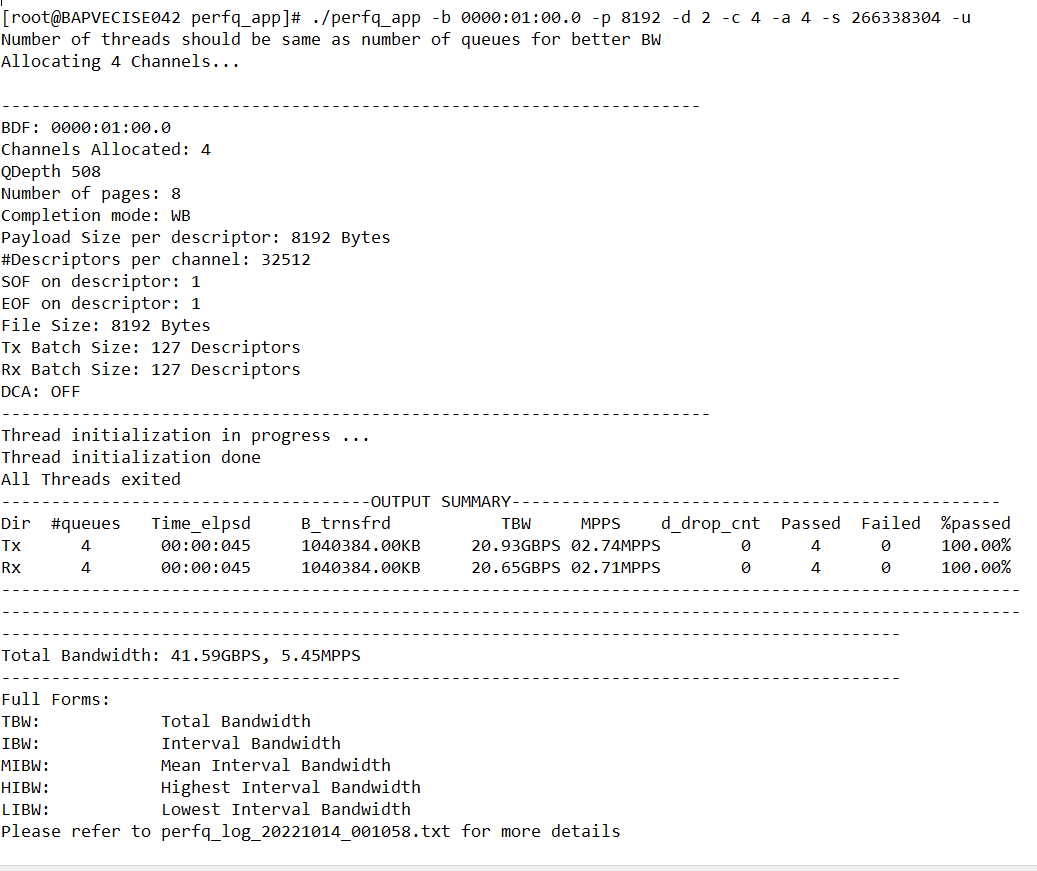

Figure 9. Performance Test: H-Tile-i option. Note: This hardware test was run with the Intel® Stratix® 10 GX H-tile PCIe Gen3 x16 configuration.

Figure 10. Performance Test: P-TileThis test was run with Intel Agilex® 7 F-Series P-Tile PCIe Gen4 x16 configuration.

Data Validation Test

[root@localhost perfq_app]#./perfq_app -b 0000:2d:00.0 -p 8192 -d 2 -c 4 -a 4 -s 268435456 -u -v Allocating 4 Channels... ---------------------------------------------------------------------- BDF: 0000:2d:00.0 Channels Allocated: 4 QDepth 508 Number of pages: 8 Completion mode: WB Payload Size per descriptor: 8192 Bytes #Descriptors per channel: 32768 SOF on descriptor: 1 EOF on descriptor: 1 File Size: 8192 Bytes Tx Batch Size: 127 Descriptors Rx Batch Size: 127 Descriptors DCA: OFF ----------------------------------------------------------------------- Thread initialization in progress ... Thread initialization done All Threads exited -------------------------------OUTPUT SUMMARY-------------------------------------------- Dir #queues Time_elpsd B_trnsfrd TBW MPPS Passed Failed %passed Tx 4 00:00:429 1048576.00KB 02.30GBPS 00.30MPPS 4 0 100.00% Rx 4 00:00:429 1048576.00KB 02.31GBPS 00.30MPPS 4 0 100.00% ------------------------------------------------------------------------------------------ -------------------------------------------------------------------------------- Full Forms: TBW: Total Bandwidth IBW: Interval Bandwidth MIBW: Mean Interval Bandwidth HIBW: Highest Interval Bandwidth LIBW: Lowest Interval Bandwidth

To enable data validation using -v option, set the software flags in user/common/mk/common.mk as follows:

- cflags += -UPERFQ_PERF

- cflags += -DPERFQ_LOAD_DATA

Note: This hardware test was run with Intel Agilex® 7 P-Tile PCIe Gen4x16 configuration.