Intel® Acceleration Stack for Intel® Xeon® CPU with FPGAs Version 1.3.1 Release Notes: Intel FPGA Programmable Acceleration Card N3000-N

Intel Provided FPGA Factory Image Packet Drop

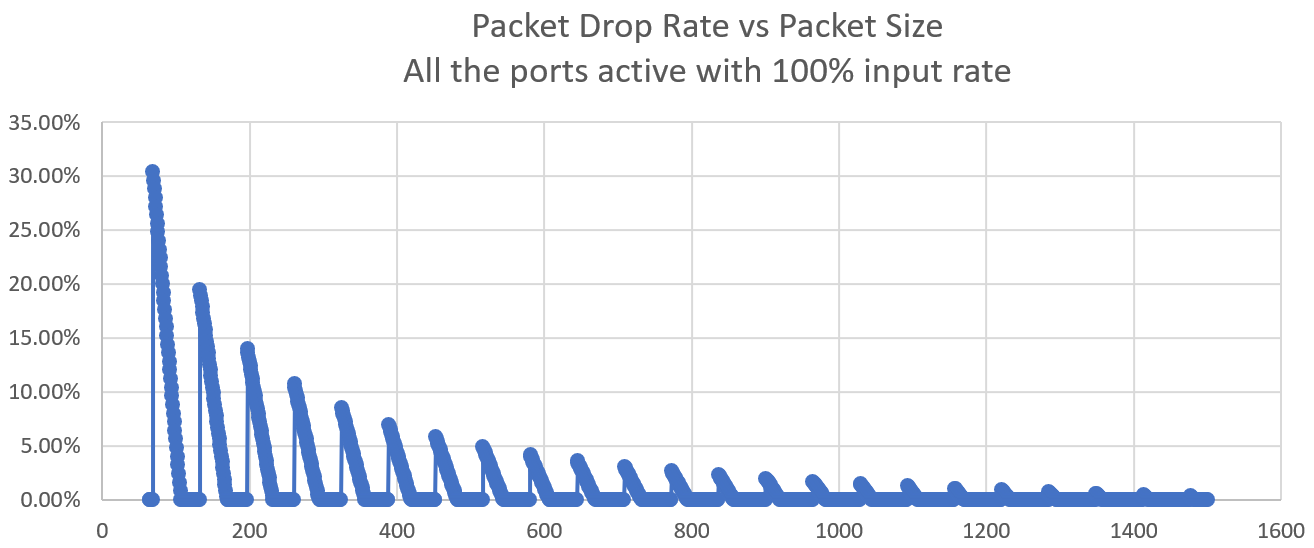

The FPGA factory image multiplexes all the Ethernet ports into one 512-bit (64 byte) bus. This bus has enough bandwidth to transport all the Ethernet ports when the packet size is a multiple of 64 bytes. When packet sizes are not multiples of 64 bytes, the last transfer of the packet on the bus carries the remainder of packet and the unused byte lanes do not carry valid data. For these packets, the bus does not have sufficient bandwidth to carry all traffic for some packet sizes. As a result of lack of bandwidth, the packet drops.

During internal tests, if all ports are active with fixed size packets that are not multiples of 64 bytes, some packet loss may occur. The worst case is 69-byte packets where the cyclic redundancy check (four bytes) is stripped off, resulting in 65 bytes transferred on the internal bus. This packet transfer takes two clock cycles. The first clock cycle transfers 64 bytes and the second clock cycle transfers one byte.