AN 907: Enabling 5G Wireless Acceleration in FlexRAN: for the Intel® FPGA Programmable Acceleration Card N3000

ID

683275

Date

9/10/2020

Public

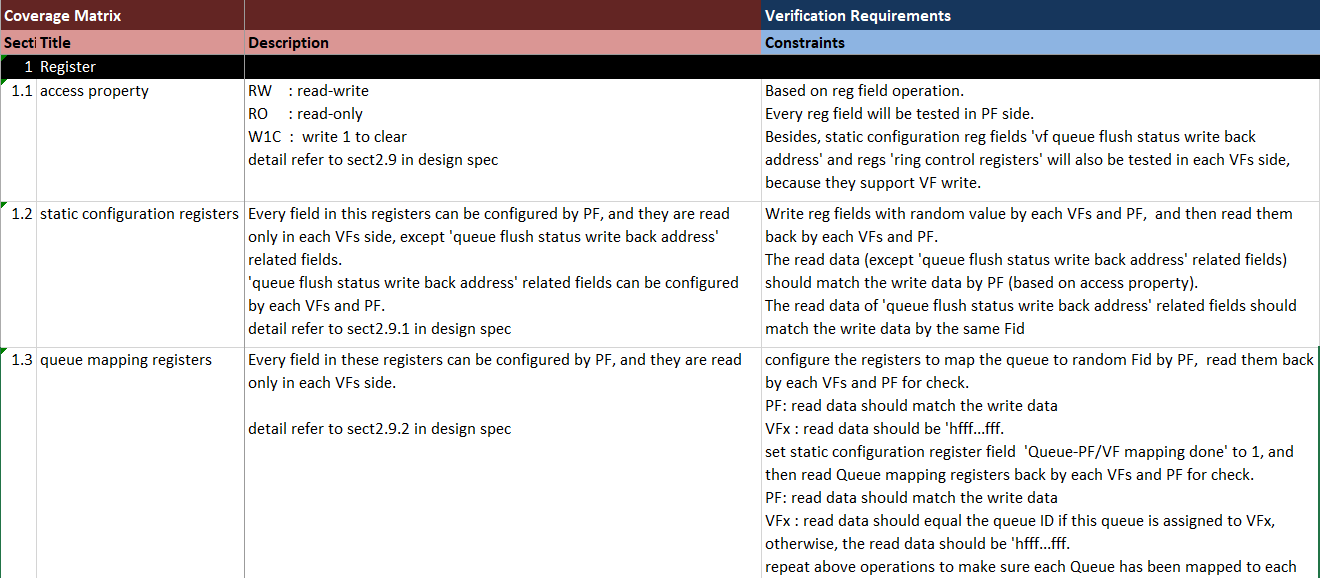

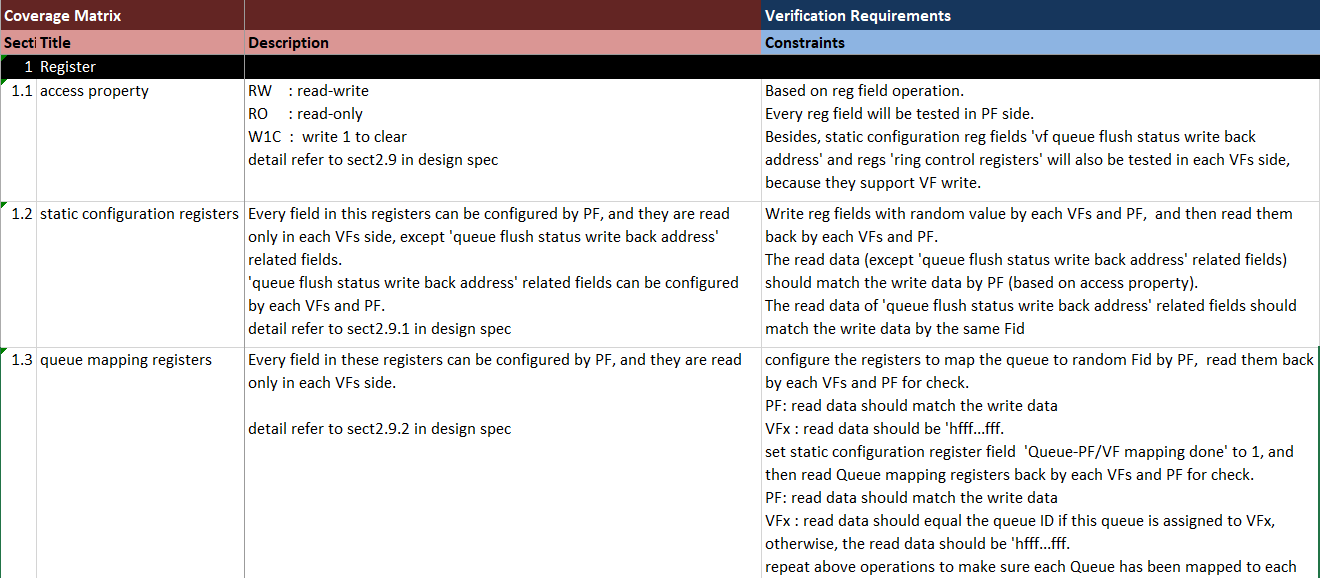

2.2.3. 5G VRAN Universal Verification Methodology

The vRAN universal verification methodology (UVM) simulation test environment for the 5G channel coder incorporates the transmitter or receiver and the DMA subsystem. The test environment does not include the preverified transaction layer packet (TLP) adapter.

The tests randomly select 2,000 test patterns from 110,000 test patterns to test the decoding function and randomly selects 2,000 test patterns from 110,000 test patterns to test the encoding function. The tests also test the randomization (and functional coverage) of system scenarios such as HARQ, physical and virtual function (PF and VF) access, queue flushing, and reset. The reference design includes the UVM test plan, 5G_LDPC_Test_Plan.xls.

Figure 11. UVM Tests