F-Tile Avalon® Streaming IP for PCI Express* User Guide

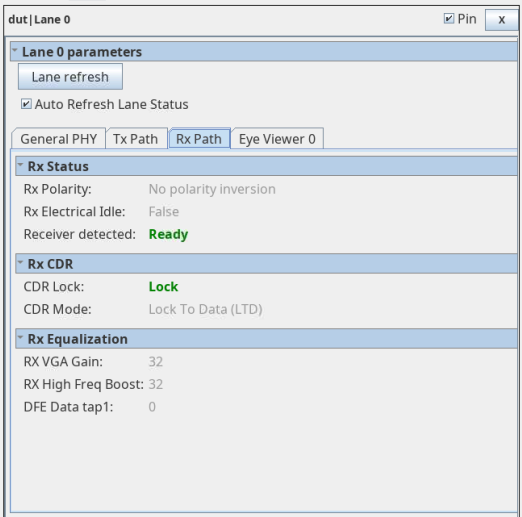

8.2.4.3.3. RX Path

This tab allows you to monitor and control the receiver settings for the channel selected.

| Parameters | Values | Descriptions | |

|---|---|---|---|

| RX Status | RX Polarity | No polarity inversion, Polarity inversion | Indicates RX polarity inversion for the selected lane. No polarity inversion: no polarity inversion on RX. Polarity inversion: polarity inversion on RX. |

| RX Electrical Idle | True, False | Indicates if RX is in electrical idle or not. True: RX is in electrical idle. False: RX is out of electrical idle. |

|

| Receiver Detected | Ready, Not Ready | Ready: Far end receiver is detected. Not Ready: Far end receiver is not detected. |

|

| RX CDR | CDR Lock | Locked, Not Locked | Indicates the CDR lock state. Locked: CDR is locked. Not Locked: CDR is not locked. |

| CDR Mode | Locked to Reference (LTR), Locked to Data (LTD) | Indicates the CDR lock mode. LTR: CDR is locked to reference clock. LTD: CDR is locked to data. |

|

| RX Equalization | RX VGA Gain | <0 to 127> |

Indicates the RX AFE VGA gain value. |

| RX High Freq Boost | <0 to 63> |

Indicates the RX AFE high frequency boost value. |

|

| DFE Data Tap1 | <0 to 63> | Indicates the adapted value of DFE tap 1. |