A newer version of this document is available. Customers should click here to go to the newest version.

2.2. Error Message Queue

The SEU_ERROR signal goes high whenever the error message queue contains one or more error messages. The signal stays high if there is an error message in the queue. The SEU_ERROR signal goes low only when the SEU error message queue is empty—after you read out all the error messages. You must set the SEU_ERROR pin function to observe the SEU_ERROR pin behavior.

To retrieve the error message queue contents, use these tools:

- Intel® Quartus® Prime Fault Injection Debugger

- Advanced SEU Detection Intel® FPGA IP

- Mailbox command

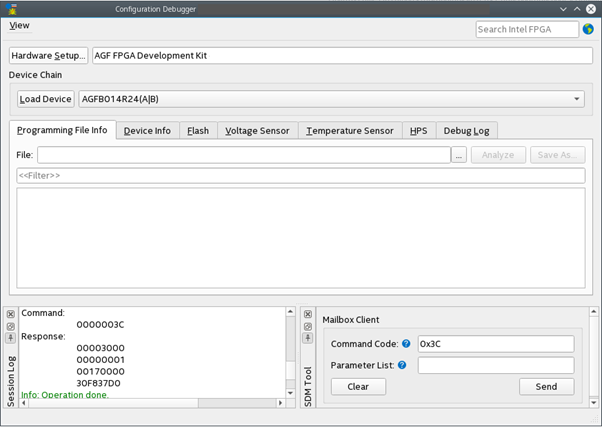

- From the Intel® Quartus® Prime menu, select Tools > Configuration Debugger.

- Select the hardware in Hardware Setup and click Load Device to select your device.

- Click View and select SDM Tool to enable the Mailbox Client window.

- Specify the Command Code and Parameter List.

- Click Send and read the response in Session Log.

The SDM firmware may not capture the SEU error if the SEU error occurs within the sectors used for partial reconfiguration, from one SEU interval before the partial reconfiguration until the partial reconfiguration completion.

| Name | Width | Bit | Description |

|---|---|---|---|

| Sector address (Most significant 32-bit word in avst_seu_source_data signal) |

32 | 31:24 | Reserved |

| 23:16 | Sector address of the error | ||

| 15:8 | Reserved | ||

| 7:4 | Error Type:

|

||

| 3:0 | Reserved | ||

| Error location2 (Least significant 32-bit word in avst_seu_source_data signal) |

32 | 31:29 | Error type:

|

| 28 | Correction Status:

|

||

| 27:25 | Reserved | ||

| 24:12 | Bit position within the frame | ||

| 11:0 | Combination of row and frame index |