Intel® Quartus® Prime Pro Edition User Guide: Programmer

ID

683039

Date

4/03/2023

Public

A newer version of this document is available. Customers should click here to go to the newest version.

2.1. Generating Primary Device Programming Files

2.2. Generating Secondary Programming Files

2.3. Enabling Bitstream Security for Intel® Stratix® 10 and Intel® Agilex™ 7 Devices

2.4. Enabling Bitstream Encryption or Compression for Intel® Arria® 10 and Intel® Cyclone® 10 GX Devices

2.5. Generating Programming Files for Partial Reconfiguration

2.6. Generating Programming Files for Intel® FPGA Devices with Hard Processor Systems

2.7. Scripting Support

2.8. Generating Programming Files Revision History

3.1. Intel® Quartus® Prime Programmer

3.2. Programming and Configuration Modes

3.3. Basic Device Configuration Steps

3.4. Specifying the Programming Hardware Setup

3.5. Programming with Flash Loaders

3.6. Verifying the Programming File Source with Project Hash

3.7. Using PR Bitstream Security Verification ( Intel® Stratix® 10 Designs)

3.8. Stand-Alone Programmer

3.9. Programmer Settings Reference

3.10. Scripting Support

3.11. Using the Intel® Quartus® Prime Programmer Revision History

3.9.1. Device & Pin Options Dialog Box

3.9.2. More Security Options Dialog Box

3.9.3. Output Files Tab Settings (Programming File Generator)

3.9.4. Input Files Tab Settings (Programming File Generator)

3.9.5. Bitstream Co-Signing Security Settings (Programming File Generator)

3.9.6. Configuration Device Tab Settings

3.9.7. Add Partition Dialog Box (Programming File Generator)

3.9.8. Add Filesystem Dialog Box (Programming File Generator)

3.9.9. Convert Programming File Dialog Box

3.9.10. Compression and Encryption Settings (Convert Programming File)

3.9.11. SOF Data Properties Dialog Box (Convert Programming File)

3.9.12. Select Devices (Flash Loader) Dialog Box

4.2. How the HPS Flash Programmer Works

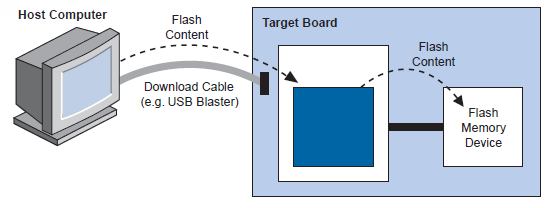

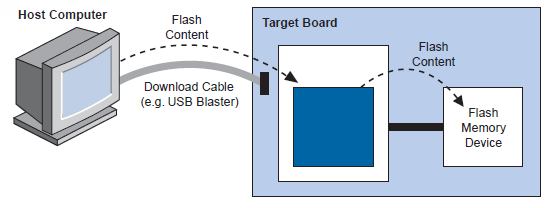

The HPS flash programmer is divided into a host and a target. The host portion runs on your computer and sends flash programming files and programming instructions over a download cable to the target. The target portion is the HPS in the SoC. The target accepts the programming data flash content and required information about the target flash memory device sent by the host. The target writes the data to the flash memory device.

Figure 36. HPS Flash Programmer

The HPS flash programmer determines the type of flash to program by sampling the boot select (BSEL) pins during cold reset; you do not need to specify the type of flash to program.