Low Latency 40G Ethernet Intel® FPGA IP Design Example User Guide: Agilex™ 5 FPGAs and SoCs

A newer version of this document is available. Customers should click here to go to the newest version.

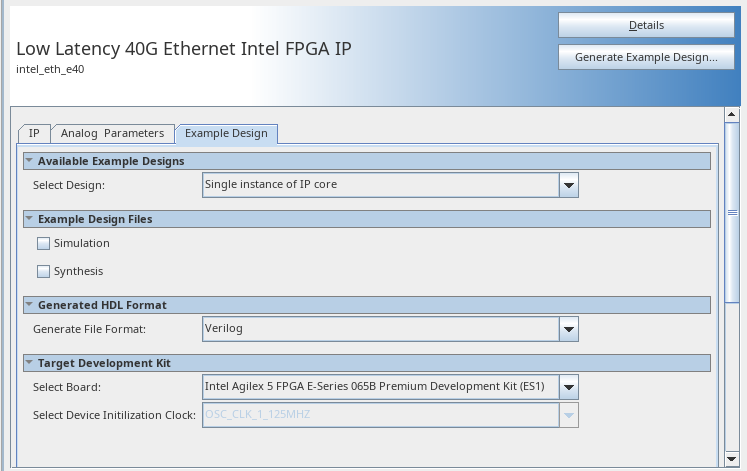

1.1.1. Design Example Parameters

| Parameter | Description |

|---|---|

| Select Design | Lists available example designs for the IP parameter settings. Single Instance of IP Core: Example designs instantiate IP instance. |

| Example Design Files | The files to generate for the different development phase.

|

| Generate File Format | The format of the RTL files for simulation—Verilog or VHDL. |

| Select Board | Provides support for various development kits listed. You can find the details of your FPGA development kits on the Intel FPGA website. If this menu is greyed out, no board is supported for the options selected, such as synthesis checked off. If you select an Intel FPGA development board, the Target Device used for design generation matches the device on the development kit. Agilex 5 FPGA E-Series 065B Premium Development Kit (ES1): This option allows you to test the design example on the selected Intel FPGA IP development kit. This option automatically selects the Target Device of A5ED065BB32AE6SR0. None: This option excludes the hardware aspects of the design example. |