External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP Design Example User Guide

ID

772632

Date

4/03/2023

Public

A newer version of this document is available. Customers should click here to go to the newest version.

1. About the External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP

2. Design Example Quick Start Guide for External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP

3. Design Example Description for External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP

4. Document Revision History for External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP Design Example User Guide

2.1. Creating an EMIF Project

2.2. Generating and Configuring the EMIF IP

2.3. Configuring DQ Pin Swizzling

2.4. Generating the Synthesizable EMIF Design Example

2.5. Generating the EMIF Design Example for Simulation

2.6. Pin Placement for Intel Agilex® 7 M-Series EMIF IP

2.7. Compiling the Intel Agilex® 7 M-Series EMIF Design Example

2.1.1.3.1. Generating a Custom Memory Preset File for DDR4

2.1.1.3.2. Guidelines for Selecting the DDR4 DRAM Component Package Type

2.1.1.3.3. Generating a Custom Memory Preset File for DDR5

2.1.1.3.4. Guidelines for Selecting the DDR5 DRAM Component Package Type

2.1.1.3.5. Generating a Custom Memory Preset File for LPDDR5

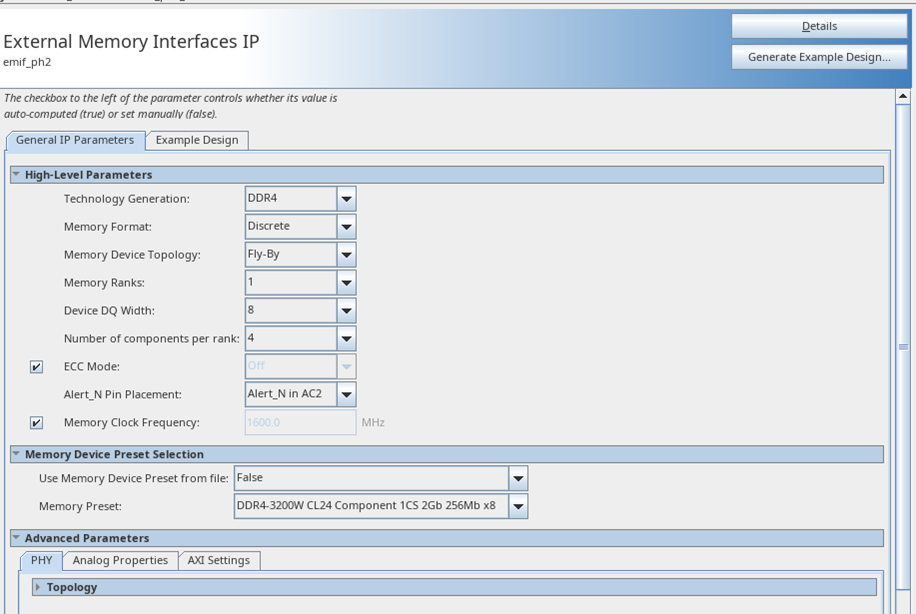

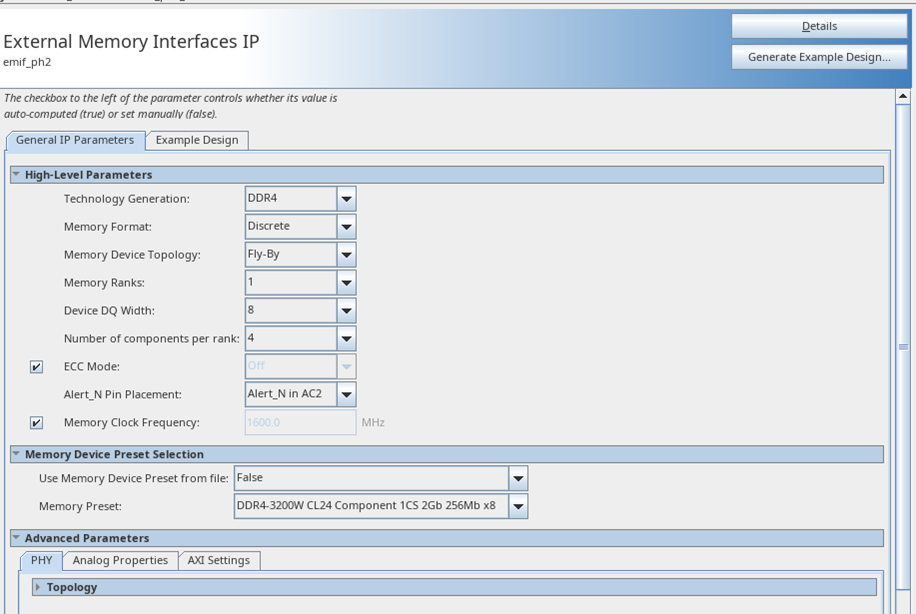

2.2.1. Intel Agilex® 7 M-Series EMIF Parameter Editor Guidelines

This topic provides high-level guidance for parameterizing the tabs in the Intel Agilex® 7 M-Series EMIF IP parameter editor.

| Parameter Editor Tab | Guidelines |

|---|---|

| High Level Parameters | Ensure that you correctly enter the following parameters:

|

| PHY | Select the desired mode to connect the EMIF IP to user logic:

|

| Analog Properties | Allows you to modify the termination and VREF settings. |

| Memory Device Preset Selection | Refer to the data sheet for your memory device and select the applicable preset. |

| Controller Configuration | Set the controller parameters according to the desired configuration and behavior for your memory controller. |

| AXI Settings | Set the AXI4 data width interface parameters according to your desired configuration. |

| Example Design | The Example Design tab lets you select which HDL to use for the top-level files, and which file sets you want the design example to generate. You should make these selections before clicking the Generate Example Design... button. The generated design example is a complete EMIF system consisting of the EMIF IP and a driver that generates random traffic to validate the memory interface. |

Figure 21. External Memory Interfaces IP Parameter Editor

For detailed information on individual parameters, refer to the appropriate protocol-specific chapter in the External Memory Interfaces Intel Agilex® 7 M-Series FPGA IP User Guide.