A newer version of this document is available. Customers should click here to go to the newest version.

3. Parameters

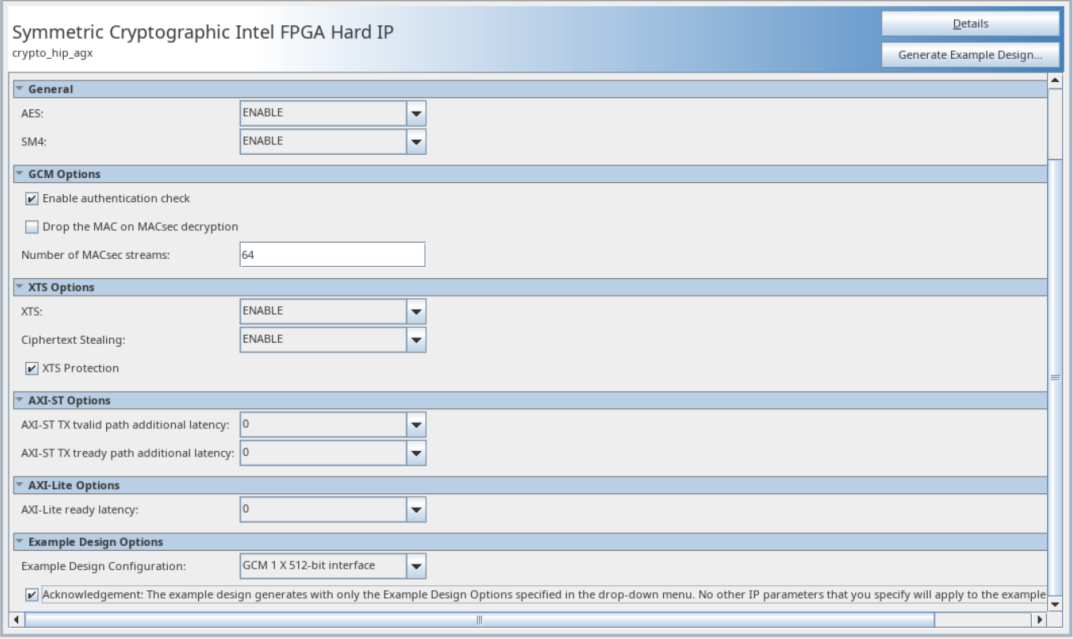

| Parameter | Supported Values | Default Setting | Description |

|---|---|---|---|

| General | |||

| AES |

|

Enable | Enable or disable the AES algorithm. |

| SM4 |

|

Enable | Enable or disable the SM4 algorithm. |

| GCM Options | |||

| Enable authentication check |

|

On | Enable or disable authentication check on a packet decryption flow. |

| Drop the MAC on MACsec decryption |

|

Off | Enable or disable dropping the MAC on decryption and not sending it out from the Symmetric Cryptographic IP core |

| Number of MACsec streams | 1-64 | 64 | Specifies the number of streams supported for MACsec profile. |

| XTS Options | |||

| XTS |

|

Enable | Enable or disable the XTS mode. |

| Cipher Text Stealing |

|

Enable | Enable or disable the Ciphertext Stealing (CTS) mode. |

| XTS+other high-frequency interleaving |

|

On | When enabled, it counts the number of tweaks/CTS/decryption within a window of time on the AXI-ST TX interface. If the threshold of either four tweaks occurs within 20 clocks, three CTS occurs within 20 cycles, or four decryption keys occur within 16 cycles, the interface is back pressured by de-asserting the tready signal. During the back pressure, logic injects a dummy encryption key cycle using channel 1023 XTS profile until the number of tweaks/CTS/decryption keys within the window drops below the threshold. This logic prevents the ICA hard IP from overflowing the number of outstanding tweaks/CTS/decryption key events that it can support. This can be disabled (turned off) to improve throughput and reduce resource usage if the traffic doesn't interleave XTS with Generic GCM or IPSEC; or frame-based interleave XTS+Generic GCM, and key is always reprogrammed for each Generic GCM packet. XTS+MACSEC interleaving is not supported in this release. |

| AXI-ST Options | |||

| AXI-ST tvalid path additional latency | 0-6 | 0 | Specifies the additional number of pipelines needed for the tvalid/tdata signal path for timing convergence. Applicable only to the responder TX side. Maximum AXI-ST Tx Latency (ready path + valid path + mode base) is up to 12.

|

| AXI-ST tready path additional latency | 0-6 | 0 | Specifies the additional number of pipelines needed for the tready signal path for timing convergence. Applicable only to the responder TX side. Maximum AXI ST TX Latency (Ready + valid signal path) is up to 13. |

| AXI-LITE Options | |||

| AXI_LITE ready latency | 0-2 | 0 | Specifies the additional number of pipelines needed for timing convergence.

Applicable only to AXI-Lite responder side. |

| Example Design Options | |||

| Example Design Configuration |

|

GCM 1 x 512-bit interface | Selects the example design options. |

| Acknowledgement: The example design generates with only the Example Design Options specified in the drop-down menu. No other IP parameters that you specify applies to the example design generation. | |||