AN 784: Partial Reconfiguration over PCI Express* Reference Design for Intel® Arria® 10 Devices

ID

683856

Date

9/24/2018

Public

1.1. Reference Design Overview

1.2. Getting Started

1.3. Reference Design Components

1.4. Compiling the Reference Design

1.5. Testing the Reference Design

1.6. Extending the Reference Design with Custom Persona

1.7. Document Revision History for AN 784: Partial Reconfiguration over PCI Express* Reference Design for Intel® Arria® 10 Devices

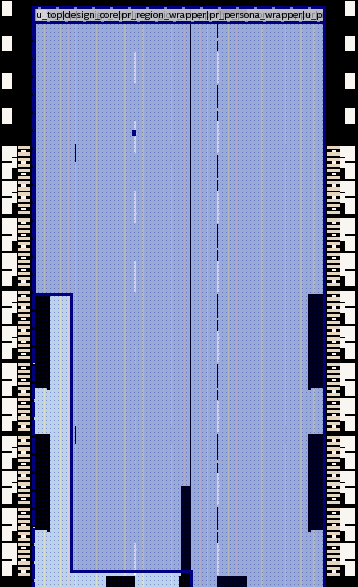

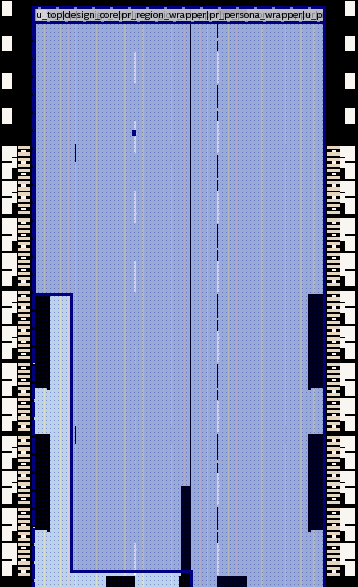

1.1.3. Floorplanning

The floorplan constraints in your partial reconfiguration design physically partitions the device. This partitioning ensures that the resources available to the PR region are the same for any persona that you implement.

To maximize the fabric amount available for the PR region, the reference design constrains the static region to the smallest possible area.

Figure 3. Reference Design Floorplan

For more information about floorplanning, refer to Floorplan the Partial Reconfiguration Design section in Volume 1 of the Intel® Quartus® Prime Pro Edition Handbook.

Related Information