AN 702: Interfacing a USB PHY to the Hard Processor System USB 2.0 OTG Controller

ID

683601

Date

9/22/2017

Public

1.4.1. Configuring the HPS USB 2.0 OTG Controller

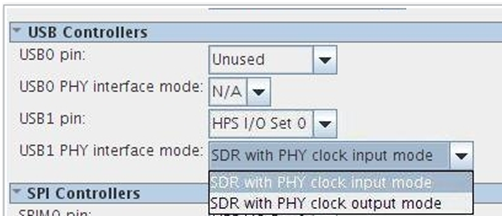

- In the Peripheral Pins tab of the Hard Processor System parameter editor, select a USB controller by setting either USB0 pin or USB1 pin to one of the available HPS I/O pin sets.

- Select the PHY interface mode in the corresponding list, USB0 PHY interface mode or USB1 PHY interface mode. Set the mode to SDR with PHY clock input mode.