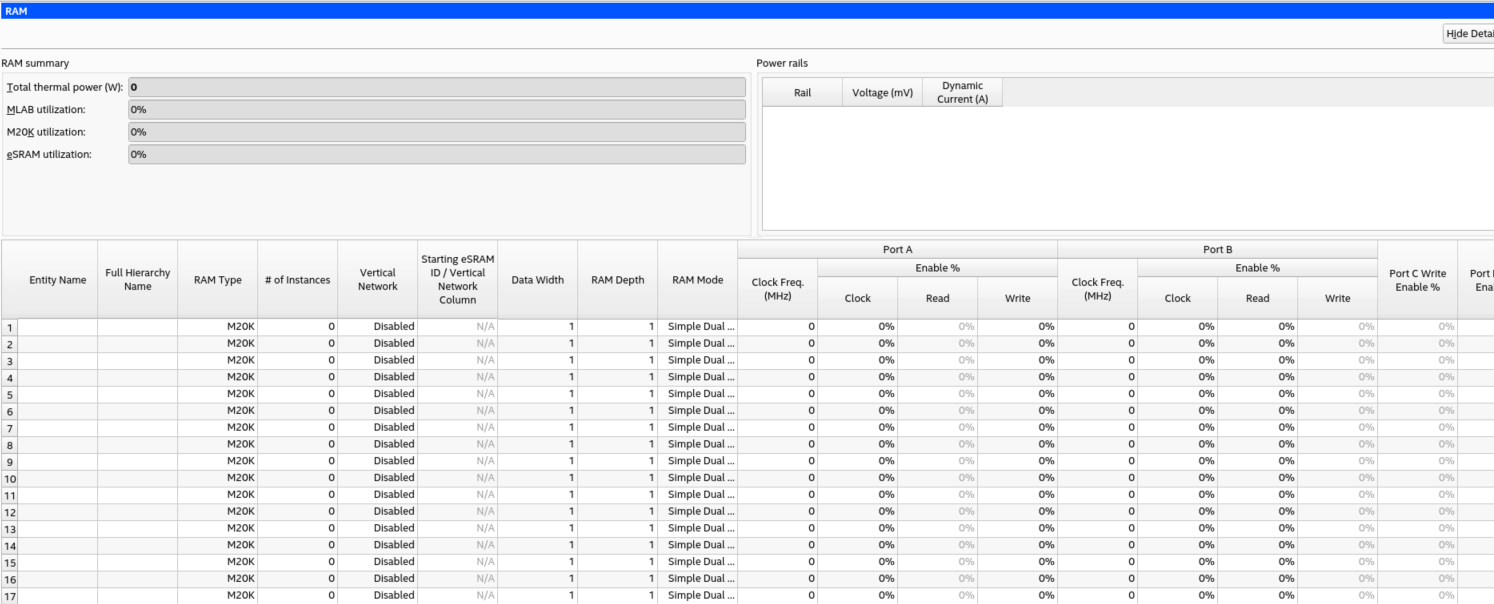

5.5. Intel® FPGA PTC - RAM Page

The Intel® FPGA PTC implements each logical RAM module with the minimum number of physical RAM blocks, in the most power-efficient way possible, based on the specified logical width and depth.

You must know how your RAM is implemented by the Intel® Quartus® Prime Compiler when you are selecting the RAM block mode. For example, if a ROM is implemented with two ports, it is considered a true dual-port memory and not a ROM. Single-port and ROM implementations use only one port. Simple dual-port and true dual-port implementations use both Port A and Port B.

- The Intel® FPGA PTC reports MLAB power in the RAM page as described above, as well as in the Power Summary table.

- In the Power Summary table, the MLAB power for Intel Agilex® 7 devices is spread across three categories: RAM, Logic, and Miscellaneous (which includes the dynamic power (W) consumed by other FPGA circuitry); this is done to be consistent with the reporting provided in the Intel® Quartus® Prime Power Analyzer.

- Some fields on the RAM page are not available for all device families.

| Column Heading | Description | |

|---|---|---|

| Entity Name | Enter a name for the RAM entity in this row. This value is optional. |

|

| Full Hierarchy Name | Specify the hierarchical path relevant to this entry. This entry is optional. When entering levels of hierarchy, the pipe character (|) denotes a level of hierarchy. | |

| RAM Type | Select the implemented RAM type. You can find the RAM type in the Type column of the Intel® Quartus® Prime Compilation Report. In the Compilation Report, select . |

|

| # of Instances | Enter the number of logical RAM instances in the module that use the same memory type and mode and have the same port parameters.

Note: This field can also accept a percentage (for example, 10%) as an input, which is used to calculate the number of instances. The "%" character informs PTC to appropriately compute and apply the resource count as an integer.

The parameters for each port are:

You can find the number of RAM blocks in either the MLAB cells or M20K blocks column of the Intel® Quartus® Prime Compilation Report. In the Compilation Report, select .

Note: The value entered into this field represents the number of logical memory blocks. Depending on the specified memory depth and data width, more than one physical memory block may be required to implement one logical block. The Power and Thermal Calculator calculates the number of physical memory blocks based on the specified memory depth and data width, such that the minimum number of physical blocks is used, and assuming the most power efficient physical configuration.

|

|

| Vertical Network | For M20K RAM Type, this field specifies whether the RAM is used in vertical network. The following options can be selected:

This column is available for Intel Agilex® 7 M-series devices only. |

|

| Starting eSRAM ID / Vertical Network Column | Specify placement information for thermal modeling. This field is applicable only when RAM Type is set to eSRAM and # RAM Blocks is set to 1, or when RAM type is set to M20K with vertical network enabled. (This column is available for Intel Agilex® 7 devices only). | |

| Data Width | Enter the width of the data for the RAM block. This value is limited based on the RAM type. You can find the width of the RAM block in the Port A Width or the Port B Width column of the Intel® Quartus® Prime Compilation Report. In the Compilation Report, select . For RAM blocks that have different widths for Port A and Port B, use the larger of the two widths. |

|

| RAM Depth | Enter the depth of the RAM block in number of words. You can find the depth of the RAM block in the Port A Depth or the Port B Depth column of the Intel® Quartus® Prime Compilation Report. In the Compilation Report, select . |

|

| RAM Mode | For MLAB and eSRAM RAM types, this field has only one possible value: Simple Dual Port. For M20K RAM type, select from the following modes:

The mode is based on how the Intel® Quartus® Prime Compiler implements the RAM. If you are unsure how your memory module is implemented, you can compile a test case in the required configuration in the Intel® Quartus® Prime software. You can find the RAM mode in the Mode column of the Intel® Quartus® Prime Compilation Report. In the Compilation Report, select . A single-port RAM has one port with a read and a write control signal. A simple dual-port RAM has one read port and one write port. A true dual-port RAM has two ports, each with a read and a write control signal. ROMs are read-only single-port RAMs. A simple quad-port RAM has a total of four ports, two read ports and two write ports.

Note: While you can use MLAB to implement more than just Simple Dual Port memory, the differences for different modes are accounted for indirectly through other input fields. For example, if one of the ports is unused, you should set its clock frequency to 0. Similarly, if MLAB is used in ROM mode, you should set Port A - Write Enable % to 0. Also, if additional registers are used for MLAB output, you should specify those on the Logic page.

|

|

| Port A - Clock Freq (MHz) | Enter the clock frequency for Port A of the RAM blocks (in MHz). This value is limited by the maximum frequency specification for the RAM type and device family. |

|

| Port A - Clock Enable % | The average percentage of time the Port A clock enable is active, regardless of activity on RAM data and address inputs. This number must be a percentage between 0% and 100%. RAM power is consumed primarily when a clock event occurs. Using a clock enable signal to disable a port when no read or write operation is occurring can result in significant power savings. |

|

| Port A - Read Enable % | Enter the percentage of time Port A of the RAM block is in read mode. This field is applicable only for true dual port RAMs. This value must be a percentage number between 0 and 100%. |

|

| Port A - Write Enable % | Enter the average percentage of time Port A of the RAM block is in write mode. This field applies only for dual port, true dual port, and quad port RAMs. This value must be a percentage number between 0 and 100%. |

|

| Port B - Clock Freq (MHz) | Enter the clock frequency for Port B of the RAM blocks (in MHz). |

|

| Port B - Clock Enable % | Enter the average percentage of time the input clock enable for Port B is active, regardless of the activity on the RAM data and address inputs. The enable percentage ranges from 0 to 100%. RAM power is consumed primarily when a clock event occurs. Using a clock-enable signal to disable a port when no read or write operation is occurring can result in significant power savings. |

|

| Port B - Read Enable % | Enter the percentage of time Port B of the RAM block is in read mode. This field is applicable only to dual port, true dual port, and quad port RAMs and ROMs. This value must be a percentage number between 0 and 100%. |

|

| Port B - Write Enable % | Enter the percentage of time Port B of the RAM block is in write mode. This field is available only for true dual-port mode. This value must be a percentage number between 0 and 100%. |

|

| Port C - Write Enable % | Enter the percentage of time the RAM block is writing to this port. In Simple Quad-Port Mode, clock and clock enable for all parts are shared and the same as Port A. This value must be a percentage number between 0 and 100%. |

|

| Port D - Read Enable % | Enter the percentage of time the RAM block is reading on this port. In Simple Quad-Port Mode, clock and clock enable for all parts are shared and the same as Port A. This value must be a percentage number between 0 and 100%. |

|

| Vertical Network Port – Read From External Memory Enable % | Enter the percentage of time the data is read from external memory into M20K blocks. This value must be a percentage number between 0 and 100%. This column is available for Intel Agilex® 7 M-Series devices only. |

|

| Vertical Network Port – Clock Enable % | Enter the average percentage of time the vertical network port clock enable is active, regardless of activity on data and address input. This value must be a percentage number between 0 and 100%. This column is available for Intel Agilex® 7 M-Series devices only. |

|

| Toggle % | The percentage of clock cycles when the block output signal changes value. This value is multiplied by the clock frequency and the enable percentage to determine the number of transitions per second. This value affects only routing power. 50% corresponds to a randomly changing signal, since half the time the signal holds the same value and thus not transition. This is considered the highest meaningful toggle rate for a RAM block. |

|

| Power (W) | Routing Power (W) | Indicates the power dissipation due to estimated routing (in W). Routing power depends on placement and routing, which is a function of design complexity. The values shown represent the routing power estimate based on observed behavior across more than 100 real-world designs. Use the Intel® Quartus® Prime Power Analyzer for accurate analysis based on the exact routing used in your design. |

| Block Power (W) | Indicates the power dissipation due to internal toggling of the RAM (in W). Use the Intel® Quartus® Prime Power Analyzer for accurate analysis based on the exact RAM modes in your design. |

|

| Total Power (W) | Indicates the estimated power (in W), based on information entered into the Intel® FPGA PTC. Total power is equal to the sum of routing power and block power. |

|

| User Comments | Enter any comments. This is an optional entry. |

|