F-Tile Avalon® Streaming Intel® FPGA IP for PCI Express* Design Example User Guide

ID

683372

Date

12/17/2021

Public

A newer version of this document is available. Customers should click here to go to the newest version.

2.1. Programmed Input/Output Design Example

2.2. Programmed Input/Output Design Example Functional Description

2.3. Programmed Input/Output Design Example Simulation Testbench

2.4. Single Root I/O Virtualization (SR-IOV) Design Example

2.5. Single Root I/O Virtualization (SR-IOV) Design Example Functional Description

2.6. Single Root I/O Virtualization (SR-IOV) Design Example Simulation Testbench

3.6.1. Running the PIO Design Example

Note: The instructions below are applicable to the F-Tile Avalon Streaming IP for PCI Express Design Example target on a custom board. Intel F-Tile development boards may be supported in a future Intel® Quartus® Prime release.

- Navigate to ./software/user/example under the design example directory.

- Compile the design example application: $ make

-

Run the test: $ sudo ./intel_fpga_pcie_link_test

You can run the Intel FPGA IP PCIe link test in manual or automatic mode. Choose from:- In automatic mode, the application automatically selects the device. The test selects the Intel PCIe device with the lowest BDF by matching the Vendor ID. The test also selects the lowest available BAR.

- In manual mode, the test queries you for the bus, device, and function number and BAR.

$ lspci -d 1172 -

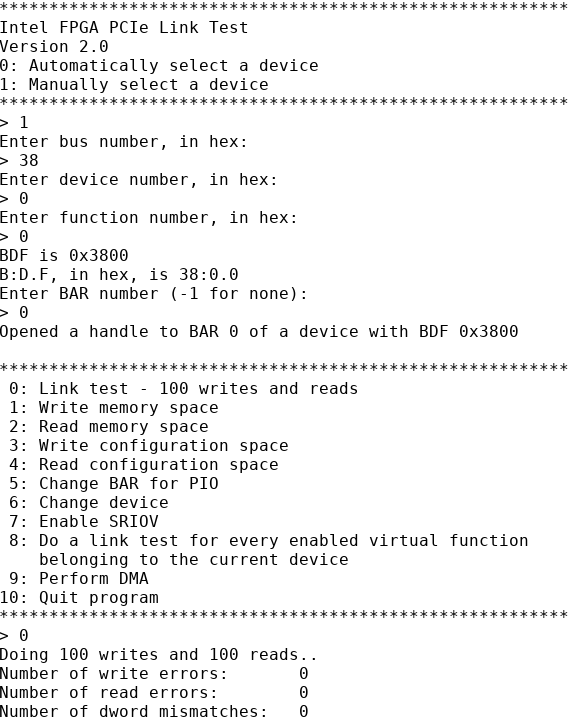

Here are sample transcripts for automatic and manual modes.Figure 23. Automatic Mode

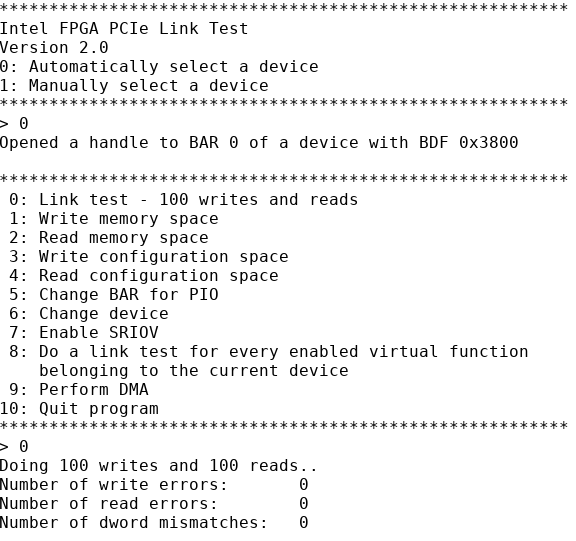

Figure 24. Manual Mode

Figure 24. Manual Mode