Intel® Quartus® Prime Pro Edition User Guide: Design Compilation

A newer version of this document is available. Customers should click here to go to the newest version.

2.3. Design Netlist Infrastructure (Beta)

The following are some significant benefits of the DNI flow in the current release:

- Access to the RTL schematic viewer with powerful interactive and analysis features.

- Access to a uniform and comprehensive scripting interface.

- Perform more granular synthesis of your design with faster iterations.

- Apply SDC constraints on RTL targets.

- Analyze timing of your design early in the flow immediately after synthesis.

DNI will support more features and capabilities in the subsequent Intel® Quartus® Prime software releases.

DNI Flow (Beta)

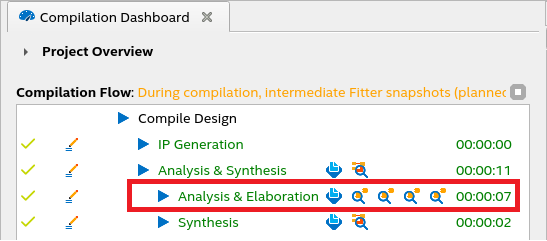

The DNI flow (beta) provides a complete and unmodified view of your design early in the DNI-based compilation flow. It serves as a platform to better analyze your design and improve it. With this Beta feature, the monolithic Analysis & Synthesis stage splits into Analysis & Elaboration and Synthesis stages.

To invoke the DNI flow, you must run the Intel® Quartus® Prime Pro Edition software with --dni option as follows:

quartus --dni <project>Once you enable the flow, the compilation dashboard gets updated. You can now access the preview modes of the Analysis & Elaboration stage, as shown in the following image:

The following diagram illustrates the detailed breakdown of the Analysis & Synthesis stage:

The Analysis & Elaboration stage is composed of a series of transformations, and you can preview your design at each stage as shown in Analysis & Elaboration and Synthesis Stages, where:

- Elaborated: Provides an unmodified preview of your design captured directly from RTL.

- Instrumented: Provides an instrumented preview with system-level debugging (debug fabric and Signal Tap logic analyzer inserted in your design).

- Constrained: Provides a design preview with SDC constraints.

- Swept: Provides a design preview with unnecessary logic removed from your design.

For information about the Synthesis stage, refer to Design Synthesis.

DNI Netlist Five-box Data Model

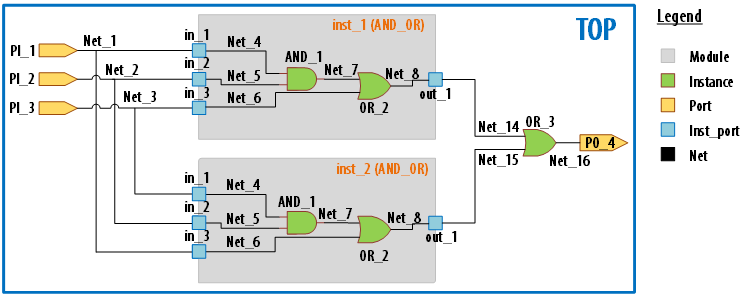

DNI introduces a conventional netlist five-box data model used in most Electronic Design Automation (EDA) tools and commonly uses Tcl commands to traverse the netlist. Consider the following two instances example:

module top (input PI_1,

input PI_2,

input PI_3,

output PO_4);

wire net_2;

wire net_3;

AND_OR inst_1(PI_1, PI_2, PI_3, net_2);

AND_OR inst_2(PI_3, PI_2, PI_1, net_3);

assign PO_4 = net_2 | net_3;

endmodule

module AND_OR (input in_1,

input in_2,

input in_3,

output out_1);

wire net_1;

assign net_1 = in_1 & in_2;

assign out_1 = net_1 | in_3;

endmoduleA DNI netlist consists of modules, instances, ports, instance ports, and nets, as shown in the following color-coded diagram:

The following table describes the core elements of this netlist data model:

| Data Model Elements | Description | Tcl Command |

|---|---|---|

| Module | A collection of connected netlist objects, such as instances, ports, nets, and instance ports. It is similar to the Verilog module or VHDL entity.

Each design has only a single top module containing a group of instances of other modules or library cells.

Note: A library cell instance is also referred to as a leaf instance.

|

– |

| Port | An I/O interface of a module. A design can have input ports, output ports, or bidirectional ports. In the DNI Data Model, PI_1, PI_2, PI_3, and PO_4 are ports. |

dni::get_ports |

| Instance | An instantiation of a module or primitive. A module instance is also referred to as a hierarchical instance, submodule, or a child of the top-level module. A module instance (submodule) may also contain a group of instances of other modules or library cells. These nested module-children instances are referred to as design hierarchies. You can build a hierarchy tree for the entire design with the root as the top module. In the DNI Data Model, inst_1, inst_2, AND_1, OR_2, and OR_3 are instances.

Note: Multiple unique objects can reference an instance if it exists in a netlist instantiated more than once.

|

dni::get_cells |

| Instance port (inst_port) | A terminal of an instance. The hierarchical I/O interfaces or leaf instances are referred to as instance ports. Their directions can be input or output.

Note: FPGA hardware does not support bidirectional signals. Hence, your design must not include any bidirectional instance ports.

In the DNI Data Model, inst_1|in_1, inst_2|AND_1|in_1 are few examples of instance ports. |

dni::get_pins |

| Net | A wire that connects terminals of instantiations or a netlist. A local net or a hierarchical net is an object within a submodule or top module to hold the connection between instance ports of child instances, instance ports of the submodule boundary, or primary ports of the top module. Hierarchical nets in the submodule and outside the top module of a hierarchical instance port have the same corresponding global or flat net. A global net or a flat net represents the connection of leaf instances or primary ports. In the DNI Data Model, Net_1, Net_2, Net_3, Net_4 and so on are nets. |

dni::get_nets |

Executing Tcl Commands

The Intel® Quartus® Prime software GUI (quartus) and Synthesis tool (quartus_syn) support Tcl commands.

Use one of the following suitable methods to execute your Tcl commands:

Intel® Quartus® Prime Software GUI (quartus)Perform the following steps in the GUI after you have enabled the DNI flow:

- On the Compilation Dashboard, run Analysis & Synthesis > Analysis & Elaboration task to generate the DNI netlist.

- Click the magnifier icon to Invoke the RTL Analyzer.

- Execute your DNI Tcl command in the Tcl Console .

- Enable the DNI flow for your project with the following command:

quartus_syn --dni --analysis_and_elaboration <project_name> - Load your design.

> quartus_syn --dni -s <... Quartus Info Message...> tcl> project_open top tcl> dni::load_design -checkpoint elaborated dms_path::sandboxes::sandbox_1239_0::design - Execute your DNI Tcl commands:

tcl> foreach_in_collection p [dni::get_pins -of_objects [dni::get_cells inst_1|out_1]] {puts [dni::get_property -name name -object $p]} a[0] a[1] o tcl> foreach_in_collection p [dni::get_pins -of_objects [dni::get_cells inst_1|out_1]] {puts [dni::get_property -name direction -object $p]} input input output tcl>